ਤੀਜੀ ਪੀੜ੍ਹੀ ਦੇ ਸੈਮੀਕੰਡਕਟਰ ਸਬਸਟਰੇਟ ਸਮੱਗਰੀ ਦੇ ਰੂਪ ਵਿੱਚ,ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ (SiC)ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਵਿੱਚ ਉੱਚ-ਆਵਿਰਤੀ ਅਤੇ ਉੱਚ-ਸ਼ਕਤੀ ਵਾਲੇ ਇਲੈਕਟ੍ਰਾਨਿਕ ਯੰਤਰਾਂ ਦੇ ਨਿਰਮਾਣ ਵਿੱਚ ਵਿਆਪਕ ਐਪਲੀਕੇਸ਼ਨ ਸੰਭਾਵਨਾਵਾਂ ਹਨ। SiC ਦੀ ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀ ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੇ ਸਬਸਟਰੇਟ ਸਮੱਗਰੀ ਦੇ ਉਤਪਾਦਨ ਵਿੱਚ ਇੱਕ ਨਿਰਣਾਇਕ ਭੂਮਿਕਾ ਨਿਭਾਉਂਦੀ ਹੈ। ਇਹ ਲੇਖ ਚੀਨ ਅਤੇ ਵਿਦੇਸ਼ਾਂ ਵਿੱਚ SiC ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀਆਂ 'ਤੇ ਖੋਜ ਦੀ ਮੌਜੂਦਾ ਸਥਿਤੀ ਨੂੰ ਪੇਸ਼ ਕਰਦਾ ਹੈ, ਕੱਟਣ, ਪੀਸਣ ਅਤੇ ਪਾਲਿਸ਼ ਕਰਨ ਦੀਆਂ ਪ੍ਰਕਿਰਿਆਵਾਂ ਦੇ ਵਿਧੀਆਂ ਦਾ ਵਿਸ਼ਲੇਸ਼ਣ ਅਤੇ ਤੁਲਨਾ ਕਰਦਾ ਹੈ, ਨਾਲ ਹੀ ਵੇਫਰ ਸਮਤਲਤਾ ਅਤੇ ਸਤਹ ਖੁਰਦਰੀ ਵਿੱਚ ਰੁਝਾਨਾਂ ਦਾ ਵੀ ਵਿਸ਼ਲੇਸ਼ਣ ਕਰਦਾ ਹੈ। ਇਹ SiC ਵੇਫਰ ਪ੍ਰੋਸੈਸਿੰਗ ਵਿੱਚ ਮੌਜੂਦਾ ਚੁਣੌਤੀਆਂ ਨੂੰ ਵੀ ਦਰਸਾਉਂਦਾ ਹੈ ਅਤੇ ਭਵਿੱਖ ਦੇ ਵਿਕਾਸ ਦਿਸ਼ਾਵਾਂ 'ਤੇ ਚਰਚਾ ਕਰਦਾ ਹੈ।

ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ (SiC)ਵੇਫਰ ਤੀਜੀ ਪੀੜ੍ਹੀ ਦੇ ਸੈਮੀਕੰਡਕਟਰ ਯੰਤਰਾਂ ਲਈ ਮਹੱਤਵਪੂਰਨ ਬੁਨਿਆਦੀ ਸਮੱਗਰੀ ਹਨ ਅਤੇ ਮਾਈਕ੍ਰੋਇਲੈਕਟ੍ਰੋਨਿਕਸ, ਪਾਵਰ ਇਲੈਕਟ੍ਰੋਨਿਕਸ, ਅਤੇ ਸੈਮੀਕੰਡਕਟਰ ਲਾਈਟਿੰਗ ਵਰਗੇ ਖੇਤਰਾਂ ਵਿੱਚ ਮਹੱਤਵਪੂਰਨ ਮਹੱਤਵ ਅਤੇ ਮਾਰਕੀਟ ਸੰਭਾਵਨਾ ਰੱਖਦੇ ਹਨ। ਬਹੁਤ ਜ਼ਿਆਦਾ ਕਠੋਰਤਾ ਅਤੇ ਰਸਾਇਣਕ ਸਥਿਰਤਾ ਦੇ ਕਾਰਨSiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ, ਰਵਾਇਤੀ ਸੈਮੀਕੰਡਕਟਰ ਪ੍ਰੋਸੈਸਿੰਗ ਵਿਧੀਆਂ ਉਹਨਾਂ ਦੀ ਮਸ਼ੀਨਿੰਗ ਲਈ ਪੂਰੀ ਤਰ੍ਹਾਂ ਢੁਕਵੀਆਂ ਨਹੀਂ ਹਨ। ਹਾਲਾਂਕਿ ਬਹੁਤ ਸਾਰੀਆਂ ਅੰਤਰਰਾਸ਼ਟਰੀ ਕੰਪਨੀਆਂ ਨੇ SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲਾਂ ਦੀ ਤਕਨੀਕੀ ਤੌਰ 'ਤੇ ਮੰਗ ਵਾਲੀ ਪ੍ਰੋਸੈਸਿੰਗ 'ਤੇ ਵਿਆਪਕ ਖੋਜ ਕੀਤੀ ਹੈ, ਪਰ ਸੰਬੰਧਿਤ ਤਕਨਾਲੋਜੀਆਂ ਨੂੰ ਪੂਰੀ ਤਰ੍ਹਾਂ ਗੁਪਤ ਰੱਖਿਆ ਜਾਂਦਾ ਹੈ।

ਹਾਲ ਹੀ ਦੇ ਸਾਲਾਂ ਵਿੱਚ, ਚੀਨ ਨੇ SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਸਮੱਗਰੀ ਅਤੇ ਉਪਕਰਣਾਂ ਦੇ ਵਿਕਾਸ ਵਿੱਚ ਯਤਨ ਵਧਾ ਦਿੱਤੇ ਹਨ। ਹਾਲਾਂਕਿ, ਦੇਸ਼ ਵਿੱਚ SiC ਡਿਵਾਈਸ ਤਕਨਾਲੋਜੀ ਦੀ ਤਰੱਕੀ ਵਰਤਮਾਨ ਵਿੱਚ ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀਆਂ ਅਤੇ ਵੇਫਰ ਗੁਣਵੱਤਾ ਵਿੱਚ ਸੀਮਾਵਾਂ ਦੁਆਰਾ ਸੀਮਤ ਹੈ। ਇਸ ਲਈ, ਚੀਨ ਲਈ SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਸਬਸਟਰੇਟਾਂ ਦੀ ਗੁਣਵੱਤਾ ਨੂੰ ਵਧਾਉਣ ਅਤੇ ਉਹਨਾਂ ਦੇ ਵਿਹਾਰਕ ਉਪਯੋਗ ਅਤੇ ਵੱਡੇ ਪੱਧਰ 'ਤੇ ਉਤਪਾਦਨ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ SiC ਪ੍ਰੋਸੈਸਿੰਗ ਸਮਰੱਥਾਵਾਂ ਵਿੱਚ ਸੁਧਾਰ ਕਰਨਾ ਜ਼ਰੂਰੀ ਹੈ।

ਮੁੱਖ ਪ੍ਰੋਸੈਸਿੰਗ ਕਦਮਾਂ ਵਿੱਚ ਸ਼ਾਮਲ ਹਨ: ਕੱਟਣਾ → ਮੋਟਾ ਪੀਸਣਾ → ਬਰੀਕ ਪੀਸਣਾ → ਮੋਟਾ ਪਾਲਿਸ਼ਿੰਗ (ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ) → ਬਰੀਕ ਪਾਲਿਸ਼ਿੰਗ (ਰਸਾਇਣਕ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ, CMP) → ਨਿਰੀਖਣ।

| ਕਦਮ | SiC ਵੇਫਰ ਪ੍ਰੋਸੈਸਿੰਗ | ਰਵਾਇਤੀ ਸੈਮੀਕੰਡਕਟਰ ਸਿੰਗਲ-ਕ੍ਰਿਸਟਲ ਮਟੀਰੀਅਲ ਪ੍ਰੋਸੈਸਿੰਗ |

| ਕੱਟਣਾ | SiC ਇੰਗਟਸ ਨੂੰ ਪਤਲੇ ਵੇਫਰਾਂ ਵਿੱਚ ਕੱਟਣ ਲਈ ਮਲਟੀ-ਵਾਇਰ ਸਾਇੰਗ ਤਕਨਾਲੋਜੀ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ | ਆਮ ਤੌਰ 'ਤੇ ਅੰਦਰੂਨੀ-ਵਿਆਸ ਜਾਂ ਬਾਹਰੀ-ਵਿਆਸ ਬਲੇਡ ਕੱਟਣ ਦੀਆਂ ਤਕਨੀਕਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ। |

| ਪੀਸਣਾ | ਕੱਟਣ ਕਾਰਨ ਆਰੇ ਦੇ ਨਿਸ਼ਾਨ ਅਤੇ ਨੁਕਸਾਨ ਵਾਲੀਆਂ ਪਰਤਾਂ ਨੂੰ ਹਟਾਉਣ ਲਈ ਮੋਟੇ ਅਤੇ ਬਰੀਕ ਪੀਸਣ ਵਿੱਚ ਵੰਡਿਆ ਗਿਆ ਹੈ। | ਪੀਸਣ ਦੇ ਤਰੀਕੇ ਵੱਖੋ-ਵੱਖਰੇ ਹੋ ਸਕਦੇ ਹਨ, ਪਰ ਟੀਚਾ ਇੱਕੋ ਹੈ। |

| ਪਾਲਿਸ਼ ਕਰਨਾ | ਮਕੈਨੀਕਲ ਅਤੇ ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ (CMP) ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ ਮੋਟਾ ਅਤੇ ਅਤਿ-ਸ਼ੁੱਧਤਾ ਵਾਲਾ ਪਾਲਿਸ਼ਿੰਗ ਸ਼ਾਮਲ ਹੈ। | ਆਮ ਤੌਰ 'ਤੇ ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ (CMP) ਸ਼ਾਮਲ ਹੁੰਦੀ ਹੈ, ਹਾਲਾਂਕਿ ਖਾਸ ਕਦਮ ਵੱਖਰੇ ਹੋ ਸਕਦੇ ਹਨ |

SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਦੀ ਕਟਾਈ

ਦੀ ਪ੍ਰੋਸੈਸਿੰਗ ਵਿੱਚSiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ, ਕੱਟਣਾ ਪਹਿਲਾ ਅਤੇ ਬਹੁਤ ਮਹੱਤਵਪੂਰਨ ਕਦਮ ਹੈ। ਕੱਟਣ ਦੀ ਪ੍ਰਕਿਰਿਆ ਦੇ ਨਤੀਜੇ ਵਜੋਂ ਵੇਫਰ ਦਾ ਧਨੁਸ਼, ਵਾਰਪ, ਅਤੇ ਕੁੱਲ ਮੋਟਾਈ ਭਿੰਨਤਾ (TTV) ਬਾਅਦ ਦੇ ਪੀਸਣ ਅਤੇ ਪਾਲਿਸ਼ ਕਰਨ ਦੇ ਕਾਰਜਾਂ ਦੀ ਗੁਣਵੱਤਾ ਅਤੇ ਪ੍ਰਭਾਵਸ਼ੀਲਤਾ ਨੂੰ ਨਿਰਧਾਰਤ ਕਰਦਾ ਹੈ।

ਕੱਟਣ ਵਾਲੇ ਔਜ਼ਾਰਾਂ ਨੂੰ ਆਕਾਰ ਅਨੁਸਾਰ ਹੀਰੇ ਦੇ ਅੰਦਰੂਨੀ ਵਿਆਸ (ID) ਆਰੇ, ਬਾਹਰੀ ਵਿਆਸ (OD) ਆਰੇ, ਬੈਂਡ ਆਰੇ ਅਤੇ ਤਾਰ ਆਰੇ ਵਿੱਚ ਸ਼੍ਰੇਣੀਬੱਧ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ। ਤਾਰ ਆਰੇ, ਬਦਲੇ ਵਿੱਚ, ਉਹਨਾਂ ਦੀ ਗਤੀ ਕਿਸਮ ਦੁਆਰਾ ਰਿਸੀਪ੍ਰੋਕੇਟਿੰਗ ਅਤੇ ਲੂਪ (ਅੰਤਹੀਣ) ਤਾਰ ਪ੍ਰਣਾਲੀਆਂ ਵਿੱਚ ਸ਼੍ਰੇਣੀਬੱਧ ਕੀਤੇ ਜਾ ਸਕਦੇ ਹਨ। ਘਸਾਉਣ ਵਾਲੇ ਦੇ ਕੱਟਣ ਦੇ ਵਿਧੀ ਦੇ ਅਧਾਰ ਤੇ, ਤਾਰ ਆਰੇ ਦੇ ਕੱਟਣ ਦੀਆਂ ਤਕਨੀਕਾਂ ਨੂੰ ਦੋ ਕਿਸਮਾਂ ਵਿੱਚ ਵੰਡਿਆ ਜਾ ਸਕਦਾ ਹੈ: ਮੁਫ਼ਤ ਘਸਾਉਣ ਵਾਲੇ ਵਾਇਰ ਆਰੇ ਅਤੇ ਸਥਿਰ ਘਸਾਉਣ ਵਾਲੇ ਹੀਰਾ ਵਾਇਰ ਆਰੇ।

1.1 ਰਵਾਇਤੀ ਕੱਟਣ ਦੇ ਤਰੀਕੇ

ਬਾਹਰੀ ਵਿਆਸ (OD) ਆਰੇ ਦੀ ਕੱਟਣ ਦੀ ਡੂੰਘਾਈ ਬਲੇਡ ਦੇ ਵਿਆਸ ਦੁਆਰਾ ਸੀਮਿਤ ਹੁੰਦੀ ਹੈ। ਕੱਟਣ ਦੀ ਪ੍ਰਕਿਰਿਆ ਦੌਰਾਨ, ਬਲੇਡ ਵਾਈਬ੍ਰੇਸ਼ਨ ਅਤੇ ਭਟਕਣ ਦਾ ਸ਼ਿਕਾਰ ਹੁੰਦਾ ਹੈ, ਜਿਸਦੇ ਨਤੀਜੇ ਵਜੋਂ ਉੱਚ ਸ਼ੋਰ ਪੱਧਰ ਅਤੇ ਮਾੜੀ ਕਠੋਰਤਾ ਹੁੰਦੀ ਹੈ। ਅੰਦਰੂਨੀ ਵਿਆਸ (ID) ਆਰੇ ਬਲੇਡ ਦੇ ਅੰਦਰੂਨੀ ਘੇਰੇ 'ਤੇ ਕੱਟਣ ਵਾਲੇ ਕਿਨਾਰੇ ਵਜੋਂ ਹੀਰੇ ਦੇ ਘਿਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹਨ। ਇਹ ਬਲੇਡ 0.2 ਮਿਲੀਮੀਟਰ ਦੇ ਪਤਲੇ ਹੋ ਸਕਦੇ ਹਨ। ਕੱਟਣ ਦੌਰਾਨ, ID ਬਲੇਡ ਤੇਜ਼ ਰਫ਼ਤਾਰ ਨਾਲ ਘੁੰਮਦਾ ਹੈ ਜਦੋਂ ਕਿ ਕੱਟਣ ਵਾਲੀ ਸਮੱਗਰੀ ਬਲੇਡ ਦੇ ਕੇਂਦਰ ਦੇ ਸਾਪੇਖਿਕ ਤੌਰ 'ਤੇ ਰੇਡੀਅਲੀ ਘੁੰਮਦੀ ਹੈ, ਇਸ ਸਾਪੇਖਿਕ ਗਤੀ ਦੁਆਰਾ ਕੱਟਣ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਦੀ ਹੈ।

ਡਾਇਮੰਡ ਬੈਂਡ ਆਰਿਆਂ ਨੂੰ ਵਾਰ-ਵਾਰ ਰੁਕਣ ਅਤੇ ਉਲਟਾਉਣ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਅਤੇ ਕੱਟਣ ਦੀ ਗਤੀ ਬਹੁਤ ਘੱਟ ਹੁੰਦੀ ਹੈ—ਆਮ ਤੌਰ 'ਤੇ 2 ਮੀਟਰ/ਸਕਿੰਟ ਤੋਂ ਵੱਧ ਨਹੀਂ ਹੁੰਦੀ। ਇਹ ਮਹੱਤਵਪੂਰਨ ਮਕੈਨੀਕਲ ਘਿਸਾਵਟ ਅਤੇ ਉੱਚ ਰੱਖ-ਰਖਾਅ ਦੇ ਖਰਚਿਆਂ ਤੋਂ ਵੀ ਪੀੜਤ ਹੁੰਦੇ ਹਨ। ਆਰੇ ਦੇ ਬਲੇਡ ਦੀ ਚੌੜਾਈ ਦੇ ਕਾਰਨ, ਕੱਟਣ ਦਾ ਘੇਰਾ ਬਹੁਤ ਛੋਟਾ ਨਹੀਂ ਹੋ ਸਕਦਾ, ਅਤੇ ਮਲਟੀ-ਸਲਾਈਸ ਕੱਟਣਾ ਸੰਭਵ ਨਹੀਂ ਹੈ। ਇਹ ਰਵਾਇਤੀ ਆਰੇ ਦੇ ਔਜ਼ਾਰ ਬੇਸ ਦੀ ਕਠੋਰਤਾ ਦੁਆਰਾ ਸੀਮਤ ਹਨ ਅਤੇ ਵਕਰ ਕੱਟ ਨਹੀਂ ਕਰ ਸਕਦੇ ਜਾਂ ਸੀਮਤ ਮੋੜਨ ਦਾ ਰੇਡੀਆਈ ਰੱਖਦੇ ਹਨ। ਇਹ ਸਿਰਫ਼ ਸਿੱਧੇ ਕੱਟ ਕਰਨ ਦੇ ਸਮਰੱਥ ਹਨ, ਚੌੜੇ ਕਰਫ ਪੈਦਾ ਕਰਦੇ ਹਨ, ਘੱਟ ਉਪਜ ਦਰ ਰੱਖਦੇ ਹਨ, ਅਤੇ ਇਸ ਤਰ੍ਹਾਂ ਕੱਟਣ ਲਈ ਅਯੋਗ ਹਨ।SiC ਕ੍ਰਿਸਟਲ.

1.2 ਮੁਫ਼ਤ ਅਬ੍ਰੈਸਿਵ ਵਾਇਰ ਸੌ ਮਲਟੀ-ਵਾਇਰ ਕਟਿੰਗ

ਫ੍ਰੀ ਅਬਰੈਸਿਵ ਵਾਇਰ ਆਰਾ ਸਲਾਈਸਿੰਗ ਤਕਨੀਕ ਤਾਰ ਦੀ ਤੇਜ਼ ਗਤੀ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਸਲਰੀ ਨੂੰ ਕੇਰਫ ਵਿੱਚ ਲੈ ਜਾਂਦੀ ਹੈ, ਜਿਸ ਨਾਲ ਸਮੱਗਰੀ ਨੂੰ ਹਟਾਉਣਾ ਸੰਭਵ ਹੁੰਦਾ ਹੈ। ਇਹ ਮੁੱਖ ਤੌਰ 'ਤੇ ਇੱਕ ਪਰਸਪਰ ਢਾਂਚੇ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ ਅਤੇ ਵਰਤਮਾਨ ਵਿੱਚ ਸਿੰਗਲ-ਕ੍ਰਿਸਟਲ ਸਿਲੀਕਾਨ ਦੀ ਕੁਸ਼ਲ ਮਲਟੀ-ਵੇਫਰ ਕਟਿੰਗ ਲਈ ਇੱਕ ਪਰਿਪੱਕ ਅਤੇ ਵਿਆਪਕ ਤੌਰ 'ਤੇ ਵਰਤਿਆ ਜਾਣ ਵਾਲਾ ਤਰੀਕਾ ਹੈ। ਹਾਲਾਂਕਿ, SiC ਕਟਿੰਗ ਵਿੱਚ ਇਸਦੀ ਵਰਤੋਂ ਦਾ ਘੱਟ ਵਿਆਪਕ ਅਧਿਐਨ ਕੀਤਾ ਗਿਆ ਹੈ।

ਮੁਫ਼ਤ ਘਸਾਉਣ ਵਾਲੇ ਤਾਰ ਆਰੇ 300 μm ਤੋਂ ਘੱਟ ਮੋਟਾਈ ਵਾਲੇ ਵੇਫਰਾਂ ਨੂੰ ਪ੍ਰੋਸੈਸ ਕਰ ਸਕਦੇ ਹਨ। ਇਹ ਘੱਟ ਕਰਫ ਨੁਕਸਾਨ ਦੀ ਪੇਸ਼ਕਸ਼ ਕਰਦੇ ਹਨ, ਘੱਟ ਹੀ ਚਿੱਪਿੰਗ ਦਾ ਕਾਰਨ ਬਣਦੇ ਹਨ, ਅਤੇ ਨਤੀਜੇ ਵਜੋਂ ਸਤਹ ਦੀ ਗੁਣਵੱਤਾ ਮੁਕਾਬਲਤਨ ਚੰਗੀ ਹੁੰਦੀ ਹੈ। ਹਾਲਾਂਕਿ, ਸਮੱਗਰੀ ਨੂੰ ਹਟਾਉਣ ਦੀ ਵਿਧੀ ਦੇ ਕਾਰਨ - ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਦੇ ਰੋਲਿੰਗ ਅਤੇ ਇੰਡੈਂਟੇਸ਼ਨ 'ਤੇ ਅਧਾਰਤ - ਵੇਫਰ ਸਤਹ ਮਹੱਤਵਪੂਰਨ ਬਕਾਇਆ ਤਣਾਅ, ਮਾਈਕ੍ਰੋਕ੍ਰੈਕਸ ਅਤੇ ਡੂੰਘੀਆਂ ਨੁਕਸਾਨ ਵਾਲੀਆਂ ਪਰਤਾਂ ਨੂੰ ਵਿਕਸਤ ਕਰਨ ਦਾ ਰੁਝਾਨ ਰੱਖਦੀ ਹੈ। ਇਸ ਨਾਲ ਵੇਫਰ ਵਾਰਪਿੰਗ ਹੁੰਦੀ ਹੈ, ਸਤਹ ਪ੍ਰੋਫਾਈਲ ਸ਼ੁੱਧਤਾ ਨੂੰ ਨਿਯੰਤਰਿਤ ਕਰਨਾ ਮੁਸ਼ਕਲ ਹੋ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਬਾਅਦ ਦੇ ਪ੍ਰੋਸੈਸਿੰਗ ਕਦਮਾਂ 'ਤੇ ਭਾਰ ਵਧਦਾ ਹੈ।

ਕੱਟਣ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਸਲਰੀ ਤੋਂ ਬਹੁਤ ਪ੍ਰਭਾਵਿਤ ਹੁੰਦੀ ਹੈ; ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਦੀ ਤਿੱਖਾਪਨ ਅਤੇ ਸਲਰੀ ਦੀ ਗਾੜ੍ਹਾਪਣ ਨੂੰ ਬਣਾਈ ਰੱਖਣਾ ਜ਼ਰੂਰੀ ਹੈ। ਸਲਰੀ ਦਾ ਇਲਾਜ ਅਤੇ ਰੀਸਾਈਕਲਿੰਗ ਮਹਿੰਗੇ ਹੁੰਦੇ ਹਨ। ਵੱਡੇ ਆਕਾਰ ਦੇ ਪਿੰਨਿਆਂ ਨੂੰ ਕੱਟਦੇ ਸਮੇਂ, ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਨੂੰ ਡੂੰਘੇ ਅਤੇ ਲੰਬੇ ਕਰਫਾਂ ਵਿੱਚ ਪ੍ਰਵੇਸ਼ ਕਰਨ ਵਿੱਚ ਮੁਸ਼ਕਲ ਆਉਂਦੀ ਹੈ। ਉਸੇ ਘਸਾਉਣ ਵਾਲੇ ਅਨਾਜ ਦੇ ਆਕਾਰ ਦੇ ਤਹਿਤ, ਕਰਫ ਦਾ ਨੁਕਸਾਨ ਸਥਿਰ-ਘਸਾਉਣ ਵਾਲੇ ਤਾਰ ਆਰਿਆਂ ਨਾਲੋਂ ਵੱਧ ਹੁੰਦਾ ਹੈ।

1.3 ਫਿਕਸਡ ਅਬ੍ਰੈਸਿਵ ਡਾਇਮੰਡ ਵਾਇਰ ਆਰਾ ਮਲਟੀ-ਵਾਇਰ ਕਟਿੰਗ

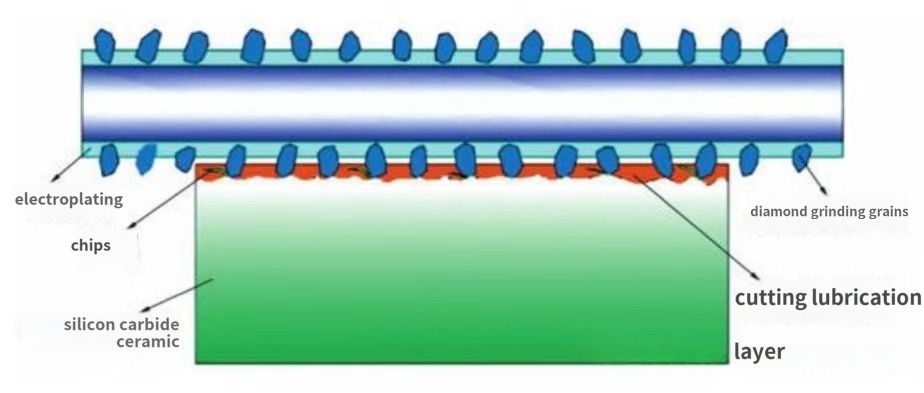

ਸਥਿਰ ਘ੍ਰਿਣਾਯੋਗ ਹੀਰੇ ਦੇ ਤਾਰ ਦੇ ਆਰੇ ਆਮ ਤੌਰ 'ਤੇ ਇਲੈਕਟ੍ਰੋਪਲੇਟਿੰਗ, ਸਿੰਟਰਿੰਗ, ਜਾਂ ਰਾਲ ਬੰਧਨ ਵਿਧੀਆਂ ਰਾਹੀਂ ਸਟੀਲ ਦੇ ਤਾਰ ਦੇ ਸਬਸਟਰੇਟ ਉੱਤੇ ਹੀਰੇ ਦੇ ਕਣਾਂ ਨੂੰ ਜੋੜ ਕੇ ਬਣਾਏ ਜਾਂਦੇ ਹਨ। ਇਲੈਕਟ੍ਰੋਪਲੇਟਿਡ ਹੀਰੇ ਦੇ ਤਾਰ ਦੇ ਆਰੇ ਤੰਗ ਕਰਫ, ਬਿਹਤਰ ਟੁਕੜੇ ਦੀ ਗੁਣਵੱਤਾ, ਉੱਚ ਕੁਸ਼ਲਤਾ, ਘੱਟ ਗੰਦਗੀ, ਅਤੇ ਉੱਚ-ਕਠੋਰਤਾ ਵਾਲੀਆਂ ਸਮੱਗਰੀਆਂ ਨੂੰ ਕੱਟਣ ਦੀ ਯੋਗਤਾ ਵਰਗੇ ਫਾਇਦੇ ਪੇਸ਼ ਕਰਦੇ ਹਨ।

ਰਿਸੀਪ੍ਰੋਕੇਟਿੰਗ ਇਲੈਕਟ੍ਰੋਪਲੇਟਿਡ ਡਾਇਮੰਡ ਵਾਇਰ ਆਰਾ ਵਰਤਮਾਨ ਵਿੱਚ SiC ਨੂੰ ਕੱਟਣ ਲਈ ਸਭ ਤੋਂ ਵੱਧ ਵਰਤਿਆ ਜਾਣ ਵਾਲਾ ਤਰੀਕਾ ਹੈ। ਚਿੱਤਰ 1 (ਇੱਥੇ ਨਹੀਂ ਦਿਖਾਇਆ ਗਿਆ) ਇਸ ਤਕਨੀਕ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਕੱਟੇ ਗਏ SiC ਵੇਫਰਾਂ ਦੀ ਸਤ੍ਹਾ ਸਮਤਲਤਾ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ। ਜਿਵੇਂ-ਜਿਵੇਂ ਕੱਟਣਾ ਅੱਗੇ ਵਧਦਾ ਹੈ, ਵੇਫਰ ਵਾਰਪੇਜ ਵਧਦਾ ਹੈ। ਇਹ ਇਸ ਲਈ ਹੈ ਕਿਉਂਕਿ ਤਾਰ ਅਤੇ ਸਮੱਗਰੀ ਵਿਚਕਾਰ ਸੰਪਰਕ ਖੇਤਰ ਵਧਦਾ ਹੈ ਜਿਵੇਂ-ਜਿਵੇਂ ਤਾਰ ਹੇਠਾਂ ਵੱਲ ਵਧਦੀ ਹੈ, ਵਿਰੋਧ ਅਤੇ ਤਾਰ ਵਾਈਬ੍ਰੇਸ਼ਨ ਵਧਦੀ ਹੈ। ਜਦੋਂ ਤਾਰ ਵੇਫਰ ਦੇ ਵੱਧ ਤੋਂ ਵੱਧ ਵਿਆਸ 'ਤੇ ਪਹੁੰਚ ਜਾਂਦੀ ਹੈ, ਤਾਂ ਵਾਈਬ੍ਰੇਸ਼ਨ ਆਪਣੇ ਸਿਖਰ 'ਤੇ ਹੁੰਦੀ ਹੈ, ਜਿਸਦੇ ਨਤੀਜੇ ਵਜੋਂ ਵੱਧ ਤੋਂ ਵੱਧ ਵਾਰਪੇਜ ਹੁੰਦਾ ਹੈ।

ਕੱਟਣ ਦੇ ਬਾਅਦ ਦੇ ਪੜਾਵਾਂ ਵਿੱਚ, ਤਾਰ ਦੇ ਪ੍ਰਵੇਗ, ਸਥਿਰ-ਗਤੀ ਦੀ ਗਤੀ, ਘਟਣ, ਰੁਕਣ ਅਤੇ ਉਲਟਣ ਦੇ ਕਾਰਨ, ਕੂਲੈਂਟ ਨਾਲ ਮਲਬੇ ਨੂੰ ਹਟਾਉਣ ਵਿੱਚ ਮੁਸ਼ਕਲਾਂ ਦੇ ਨਾਲ, ਵੇਫਰ ਦੀ ਸਤ੍ਹਾ ਦੀ ਗੁਣਵੱਤਾ ਵਿਗੜ ਜਾਂਦੀ ਹੈ। ਤਾਰ ਉਲਟਾਉਣ ਅਤੇ ਗਤੀ ਦੇ ਉਤਰਾਅ-ਚੜ੍ਹਾਅ, ਅਤੇ ਨਾਲ ਹੀ ਤਾਰ 'ਤੇ ਵੱਡੇ ਹੀਰੇ ਦੇ ਕਣ, ਸਤ੍ਹਾ 'ਤੇ ਖੁਰਚਣ ਦੇ ਮੁੱਖ ਕਾਰਨ ਹਨ।

1.4 ਕੋਲਡ ਸੈਪਰੇਸ਼ਨ ਤਕਨਾਲੋਜੀ

SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲਾਂ ਦਾ ਠੰਡਾ ਵੱਖਰਾਕਰਨ ਤੀਜੀ ਪੀੜ੍ਹੀ ਦੇ ਸੈਮੀਕੰਡਕਟਰ ਸਮੱਗਰੀ ਪ੍ਰੋਸੈਸਿੰਗ ਦੇ ਖੇਤਰ ਵਿੱਚ ਇੱਕ ਨਵੀਨਤਾਕਾਰੀ ਪ੍ਰਕਿਰਿਆ ਹੈ। ਹਾਲ ਹੀ ਦੇ ਸਾਲਾਂ ਵਿੱਚ, ਇਸਨੇ ਉਪਜ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਅਤੇ ਸਮੱਗਰੀ ਦੇ ਨੁਕਸਾਨ ਨੂੰ ਘਟਾਉਣ ਵਿੱਚ ਇਸਦੇ ਮਹੱਤਵਪੂਰਨ ਫਾਇਦਿਆਂ ਦੇ ਕਾਰਨ ਮਹੱਤਵਪੂਰਨ ਧਿਆਨ ਖਿੱਚਿਆ ਹੈ। ਤਕਨਾਲੋਜੀ ਦਾ ਵਿਸ਼ਲੇਸ਼ਣ ਤਿੰਨ ਪਹਿਲੂਆਂ ਤੋਂ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ: ਕਾਰਜਸ਼ੀਲ ਸਿਧਾਂਤ, ਪ੍ਰਕਿਰਿਆ ਪ੍ਰਵਾਹ, ਅਤੇ ਮੁੱਖ ਫਾਇਦੇ।

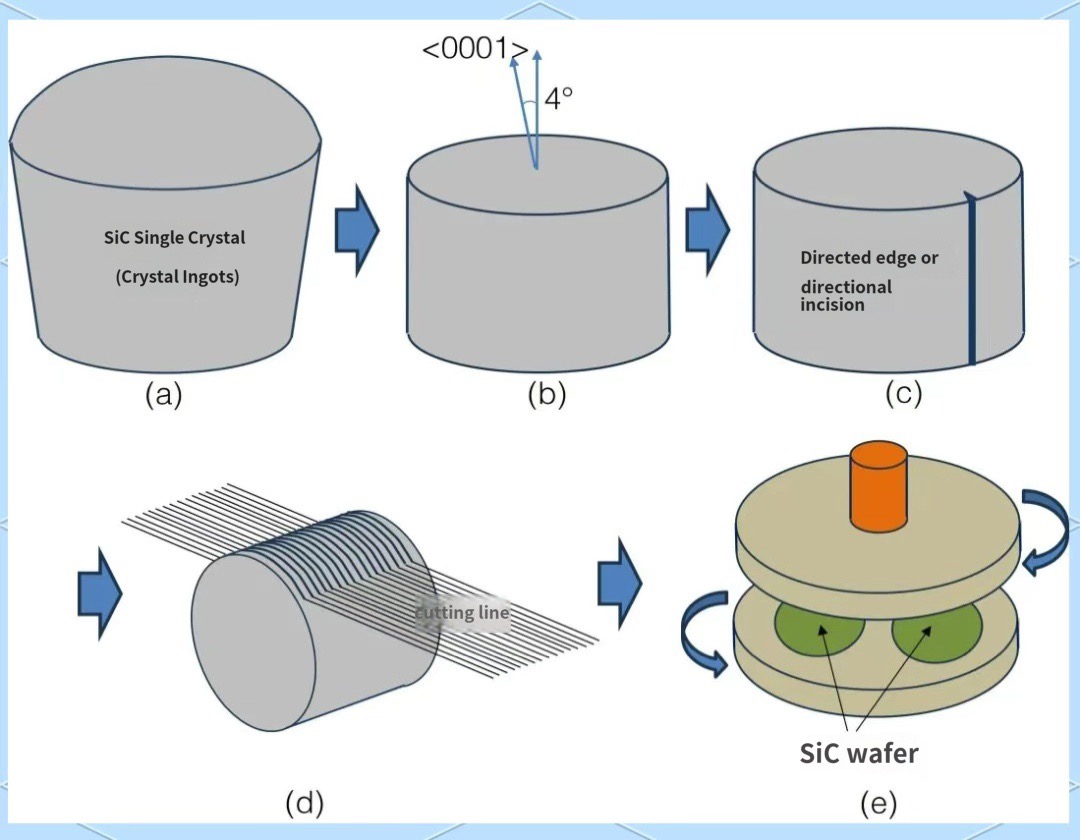

ਕ੍ਰਿਸਟਲ ਓਰੀਐਂਟੇਸ਼ਨ ਨਿਰਧਾਰਨ ਅਤੇ ਬਾਹਰੀ ਵਿਆਸ ਪੀਸਣਾ: ਪ੍ਰੋਸੈਸਿੰਗ ਤੋਂ ਪਹਿਲਾਂ, SiC ਇੰਗੋਟ ਦੀ ਕ੍ਰਿਸਟਲ ਓਰੀਐਂਟੇਸ਼ਨ ਨਿਰਧਾਰਤ ਕੀਤੀ ਜਾਣੀ ਚਾਹੀਦੀ ਹੈ। ਫਿਰ ਇੰਗੋਟ ਨੂੰ ਬਾਹਰੀ ਵਿਆਸ ਪੀਸਣ ਦੁਆਰਾ ਇੱਕ ਸਿਲੰਡਰ ਬਣਤਰ (ਆਮ ਤੌਰ 'ਤੇ SiC ਪੱਕ ਕਿਹਾ ਜਾਂਦਾ ਹੈ) ਵਿੱਚ ਆਕਾਰ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ। ਇਹ ਕਦਮ ਬਾਅਦ ਵਿੱਚ ਦਿਸ਼ਾਤਮਕ ਕੱਟਣ ਅਤੇ ਕੱਟਣ ਲਈ ਨੀਂਹ ਰੱਖਦਾ ਹੈ।

ਮਲਟੀ-ਵਾਇਰ ਕਟਿੰਗ: ਇਹ ਵਿਧੀ ਸਿਲੰਡਰ ਇਨਗੌਟ ਨੂੰ ਕੱਟਣ ਲਈ ਕੱਟਣ ਵਾਲੀਆਂ ਤਾਰਾਂ ਦੇ ਨਾਲ ਮਿਲਾ ਕੇ ਘ੍ਰਿਣਾਯੋਗ ਕਣਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦੀ ਹੈ। ਹਾਲਾਂਕਿ, ਇਹ ਮਹੱਤਵਪੂਰਨ ਕਰਫ ਨੁਕਸਾਨ ਅਤੇ ਸਤਹ ਅਸਮਾਨਤਾ ਦੇ ਮੁੱਦਿਆਂ ਤੋਂ ਪੀੜਤ ਹੈ।

ਲੇਜ਼ਰ ਕਟਿੰਗ ਤਕਨਾਲੋਜੀ: ਕ੍ਰਿਸਟਲ ਦੇ ਅੰਦਰ ਇੱਕ ਸੋਧੀ ਹੋਈ ਪਰਤ ਬਣਾਉਣ ਲਈ ਇੱਕ ਲੇਜ਼ਰ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਜਿਸ ਤੋਂ ਪਤਲੇ ਟੁਕੜਿਆਂ ਨੂੰ ਵੱਖ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ। ਇਹ ਪਹੁੰਚ ਸਮੱਗਰੀ ਦੇ ਨੁਕਸਾਨ ਨੂੰ ਘਟਾਉਂਦੀ ਹੈ ਅਤੇ ਪ੍ਰੋਸੈਸਿੰਗ ਕੁਸ਼ਲਤਾ ਨੂੰ ਵਧਾਉਂਦੀ ਹੈ, ਜਿਸ ਨਾਲ ਇਹ SiC ਵੇਫਰ ਕਟਿੰਗ ਲਈ ਇੱਕ ਵਾਅਦਾ ਕਰਨ ਵਾਲੀ ਨਵੀਂ ਦਿਸ਼ਾ ਬਣ ਜਾਂਦੀ ਹੈ।

ਕੱਟਣ ਦੀ ਪ੍ਰਕਿਰਿਆ ਦਾ ਅਨੁਕੂਲਨ

ਫਿਕਸਡ ਅਬ੍ਰੈਸਿਵ ਮਲਟੀ-ਵਾਇਰ ਕਟਿੰਗ: ਇਹ ਵਰਤਮਾਨ ਵਿੱਚ ਮੁੱਖ ਧਾਰਾ ਤਕਨਾਲੋਜੀ ਹੈ, ਜੋ SiC ਦੀਆਂ ਉੱਚ ਕਠੋਰਤਾ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਲਈ ਢੁਕਵੀਂ ਹੈ।

ਇਲੈਕਟ੍ਰੀਕਲ ਡਿਸਚਾਰਜ ਮਸ਼ੀਨਿੰਗ (EDM) ਅਤੇ ਕੋਲਡ ਸੇਪਰੇਸ਼ਨ ਤਕਨਾਲੋਜੀ: ਇਹ ਵਿਧੀਆਂ ਖਾਸ ਜ਼ਰੂਰਤਾਂ ਦੇ ਅਨੁਸਾਰ ਵਿਭਿੰਨ ਹੱਲ ਪ੍ਰਦਾਨ ਕਰਦੀਆਂ ਹਨ।

ਪਾਲਿਸ਼ਿੰਗ ਪ੍ਰਕਿਰਿਆ: ਸਮੱਗਰੀ ਨੂੰ ਹਟਾਉਣ ਦੀ ਦਰ ਅਤੇ ਸਤ੍ਹਾ ਦੇ ਨੁਕਸਾਨ ਨੂੰ ਸੰਤੁਲਿਤ ਕਰਨਾ ਜ਼ਰੂਰੀ ਹੈ। ਸਤ੍ਹਾ ਦੀ ਇਕਸਾਰਤਾ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਲਈ ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ (CMP) ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਂਦੀ ਹੈ।

ਰੀਅਲ-ਟਾਈਮ ਨਿਗਰਾਨੀ: ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ ਦੀ ਅਸਲ-ਸਮੇਂ ਵਿੱਚ ਨਿਗਰਾਨੀ ਕਰਨ ਲਈ ਔਨਲਾਈਨ ਨਿਰੀਖਣ ਤਕਨਾਲੋਜੀਆਂ ਪੇਸ਼ ਕੀਤੀਆਂ ਗਈਆਂ ਹਨ।

ਲੇਜ਼ਰ ਸਲਾਈਸਿੰਗ: ਇਹ ਤਕਨੀਕ ਕਰਫ ਦੇ ਨੁਕਸਾਨ ਨੂੰ ਘਟਾਉਂਦੀ ਹੈ ਅਤੇ ਪ੍ਰੋਸੈਸਿੰਗ ਚੱਕਰਾਂ ਨੂੰ ਛੋਟਾ ਕਰਦੀ ਹੈ, ਹਾਲਾਂਕਿ ਥਰਮਲ ਪ੍ਰਭਾਵਿਤ ਜ਼ੋਨ ਇੱਕ ਚੁਣੌਤੀ ਬਣਿਆ ਹੋਇਆ ਹੈ।

ਹਾਈਬ੍ਰਿਡ ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀਆਂ: ਮਕੈਨੀਕਲ ਅਤੇ ਰਸਾਇਣਕ ਤਰੀਕਿਆਂ ਦਾ ਸੁਮੇਲ ਪ੍ਰੋਸੈਸਿੰਗ ਕੁਸ਼ਲਤਾ ਨੂੰ ਵਧਾਉਂਦਾ ਹੈ।

ਇਸ ਤਕਨਾਲੋਜੀ ਨੇ ਪਹਿਲਾਂ ਹੀ ਉਦਯੋਗਿਕ ਉਪਯੋਗ ਪ੍ਰਾਪਤ ਕਰ ਲਿਆ ਹੈ। ਉਦਾਹਰਣ ਵਜੋਂ, ਇਨਫਾਈਨਓਨ ਨੇ ਸਿਲਟੈਕਟਰਾ ਪ੍ਰਾਪਤ ਕੀਤਾ ਅਤੇ ਹੁਣ 8-ਇੰਚ ਵੇਫਰਾਂ ਦੇ ਵੱਡੇ ਉਤਪਾਦਨ ਦਾ ਸਮਰਥਨ ਕਰਨ ਵਾਲੇ ਮੁੱਖ ਪੇਟੈਂਟ ਰੱਖਦਾ ਹੈ। ਚੀਨ ਵਿੱਚ, ਡੇਲੋਂਗ ਲੇਜ਼ਰ ਵਰਗੀਆਂ ਕੰਪਨੀਆਂ ਨੇ 6-ਇੰਚ ਵੇਫਰ ਪ੍ਰੋਸੈਸਿੰਗ ਲਈ ਪ੍ਰਤੀ ਇੰਗਟ 30 ਵੇਫਰ ਦੀ ਆਉਟਪੁੱਟ ਕੁਸ਼ਲਤਾ ਪ੍ਰਾਪਤ ਕੀਤੀ ਹੈ, ਜੋ ਕਿ ਰਵਾਇਤੀ ਤਰੀਕਿਆਂ ਨਾਲੋਂ 40% ਸੁਧਾਰ ਨੂੰ ਦਰਸਾਉਂਦੀ ਹੈ।

ਜਿਵੇਂ-ਜਿਵੇਂ ਘਰੇਲੂ ਉਪਕਰਣ ਨਿਰਮਾਣ ਵਿੱਚ ਤੇਜ਼ੀ ਆ ਰਹੀ ਹੈ, ਇਸ ਤਕਨਾਲੋਜੀ ਦੇ SiC ਸਬਸਟਰੇਟ ਪ੍ਰੋਸੈਸਿੰਗ ਲਈ ਮੁੱਖ ਧਾਰਾ ਦਾ ਹੱਲ ਬਣਨ ਦੀ ਉਮੀਦ ਹੈ। ਸੈਮੀਕੰਡਕਟਰ ਸਮੱਗਰੀ ਦੇ ਵਧਦੇ ਵਿਆਸ ਦੇ ਨਾਲ, ਰਵਾਇਤੀ ਕੱਟਣ ਦੇ ਤਰੀਕੇ ਪੁਰਾਣੇ ਹੋ ਗਏ ਹਨ। ਮੌਜੂਦਾ ਵਿਕਲਪਾਂ ਵਿੱਚੋਂ, ਰਿਸੀਪ੍ਰੋਕੇਟਿੰਗ ਡਾਇਮੰਡ ਵਾਇਰ ਆਰਾ ਤਕਨਾਲੋਜੀ ਸਭ ਤੋਂ ਵੱਧ ਵਾਅਦਾ ਕਰਨ ਵਾਲੀਆਂ ਐਪਲੀਕੇਸ਼ਨ ਸੰਭਾਵਨਾਵਾਂ ਦਰਸਾਉਂਦੀ ਹੈ। ਲੇਜ਼ਰ ਕਟਿੰਗ, ਇੱਕ ਉੱਭਰ ਰਹੀ ਤਕਨੀਕ ਦੇ ਰੂਪ ਵਿੱਚ, ਮਹੱਤਵਪੂਰਨ ਫਾਇਦੇ ਪ੍ਰਦਾਨ ਕਰਦੀ ਹੈ ਅਤੇ ਭਵਿੱਖ ਵਿੱਚ ਪ੍ਰਾਇਮਰੀ ਕੱਟਣ ਦਾ ਤਰੀਕਾ ਬਣਨ ਦੀ ਉਮੀਦ ਹੈ।

2,SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਪੀਸਣਾ

ਤੀਜੀ ਪੀੜ੍ਹੀ ਦੇ ਸੈਮੀਕੰਡਕਟਰਾਂ ਦੇ ਪ੍ਰਤੀਨਿਧੀ ਵਜੋਂ, ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ (SiC) ਆਪਣੇ ਚੌੜੇ ਬੈਂਡਗੈਪ, ਉੱਚ ਬ੍ਰੇਕਡਾਊਨ ਇਲੈਕਟ੍ਰਿਕ ਫੀਲਡ, ਉੱਚ ਸੰਤ੍ਰਿਪਤਾ ਇਲੈਕਟ੍ਰੌਨ ਡ੍ਰਿਫਟ ਵੇਗ, ਅਤੇ ਸ਼ਾਨਦਾਰ ਥਰਮਲ ਚਾਲਕਤਾ ਦੇ ਕਾਰਨ ਮਹੱਤਵਪੂਰਨ ਫਾਇਦੇ ਪ੍ਰਦਾਨ ਕਰਦਾ ਹੈ। ਇਹ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ SiC ਨੂੰ ਉੱਚ-ਵੋਲਟੇਜ ਐਪਲੀਕੇਸ਼ਨਾਂ (ਜਿਵੇਂ ਕਿ, 1200V ਵਾਤਾਵਰਣ) ਵਿੱਚ ਵਿਸ਼ੇਸ਼ ਤੌਰ 'ਤੇ ਲਾਭਦਾਇਕ ਬਣਾਉਂਦੀਆਂ ਹਨ। SiC ਸਬਸਟਰੇਟਾਂ ਲਈ ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀ ਡਿਵਾਈਸ ਫੈਬਰੀਕੇਸ਼ਨ ਦਾ ਇੱਕ ਬੁਨਿਆਦੀ ਹਿੱਸਾ ਹੈ। ਸਬਸਟਰੇਟ ਦੀ ਸਤਹ ਗੁਣਵੱਤਾ ਅਤੇ ਸ਼ੁੱਧਤਾ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਗੁਣਵੱਤਾ ਅਤੇ ਅੰਤਮ ਡਿਵਾਈਸ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਨੂੰ ਪ੍ਰਭਾਵਤ ਕਰਦੀ ਹੈ।

ਪੀਸਣ ਦੀ ਪ੍ਰਕਿਰਿਆ ਦਾ ਮੁੱਖ ਉਦੇਸ਼ ਕੱਟਣ ਦੌਰਾਨ ਸਤ੍ਹਾ ਦੇ ਆਰੇ ਦੇ ਨਿਸ਼ਾਨ ਅਤੇ ਨੁਕਸਾਨ ਵਾਲੀਆਂ ਪਰਤਾਂ ਨੂੰ ਹਟਾਉਣਾ ਹੈ, ਅਤੇ ਕੱਟਣ ਦੀ ਪ੍ਰਕਿਰਿਆ ਦੁਆਰਾ ਪੈਦਾ ਹੋਏ ਵਿਗਾੜ ਨੂੰ ਠੀਕ ਕਰਨਾ ਹੈ। SiC ਦੀ ਬਹੁਤ ਜ਼ਿਆਦਾ ਕਠੋਰਤਾ ਨੂੰ ਦੇਖਦੇ ਹੋਏ, ਪੀਸਣ ਲਈ ਬੋਰਾਨ ਕਾਰਬਾਈਡ ਜਾਂ ਹੀਰਾ ਵਰਗੇ ਸਖ਼ਤ ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਦੀ ਵਰਤੋਂ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਰਵਾਇਤੀ ਪੀਸਣ ਨੂੰ ਆਮ ਤੌਰ 'ਤੇ ਮੋਟੇ ਪੀਸਣ ਅਤੇ ਬਰੀਕ ਪੀਸਣ ਵਿੱਚ ਵੰਡਿਆ ਜਾਂਦਾ ਹੈ।

2.1 ਮੋਟਾ ਅਤੇ ਬਾਰੀਕ ਪੀਸਣਾ

ਪੀਸਣ ਨੂੰ ਘਸਾਉਣ ਵਾਲੇ ਕਣਾਂ ਦੇ ਆਕਾਰ ਦੇ ਆਧਾਰ 'ਤੇ ਸ਼੍ਰੇਣੀਬੱਧ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ:

ਮੋਟਾ ਪੀਸਣਾ: ਕੱਟਣ ਦੌਰਾਨ ਆਰੇ ਦੇ ਨਿਸ਼ਾਨ ਅਤੇ ਨੁਕਸਾਨ ਵਾਲੀਆਂ ਪਰਤਾਂ ਨੂੰ ਹਟਾਉਣ ਲਈ ਮੁੱਖ ਤੌਰ 'ਤੇ ਵੱਡੇ ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਜਿਸ ਨਾਲ ਪ੍ਰੋਸੈਸਿੰਗ ਕੁਸ਼ਲਤਾ ਵਿੱਚ ਸੁਧਾਰ ਹੁੰਦਾ ਹੈ।

ਬਾਰੀਕ ਪੀਸਣਾ: ਮੋਟੇ ਪੀਸਣ ਨਾਲ ਬਚੀ ਨੁਕਸਾਨ ਵਾਲੀ ਪਰਤ ਨੂੰ ਹਟਾਉਣ, ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ ਨੂੰ ਘਟਾਉਣ ਅਤੇ ਸਤ੍ਹਾ ਦੀ ਗੁਣਵੱਤਾ ਵਧਾਉਣ ਲਈ ਬਾਰੀਕ ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ।

ਬਹੁਤ ਸਾਰੇ ਘਰੇਲੂ SiC ਸਬਸਟਰੇਟ ਨਿਰਮਾਤਾ ਵੱਡੇ ਪੱਧਰ 'ਤੇ ਉਤਪਾਦਨ ਪ੍ਰਕਿਰਿਆਵਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹਨ। ਇੱਕ ਆਮ ਵਿਧੀ ਵਿੱਚ ਕਾਸਟ ਆਇਰਨ ਪਲੇਟ ਅਤੇ ਮੋਨੋਕ੍ਰਿਸਟਲਾਈਨ ਡਾਇਮੰਡ ਸਲਰੀ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਦੋ-ਪਾਸੜ ਪੀਸਣਾ ਸ਼ਾਮਲ ਹੁੰਦਾ ਹੈ। ਇਹ ਪ੍ਰਕਿਰਿਆ ਤਾਰਾਂ ਨੂੰ ਕੱਟਣ ਨਾਲ ਬਚੀ ਨੁਕਸਾਨ ਦੀ ਪਰਤ ਨੂੰ ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਢੰਗ ਨਾਲ ਹਟਾਉਂਦੀ ਹੈ, ਵੇਫਰ ਦੀ ਸ਼ਕਲ ਨੂੰ ਠੀਕ ਕਰਦੀ ਹੈ, ਅਤੇ TTV (ਕੁੱਲ ਮੋਟਾਈ ਭਿੰਨਤਾ), ਧਨੁਸ਼ ਅਤੇ ਵਾਰਪ ਨੂੰ ਘਟਾਉਂਦੀ ਹੈ। ਸਮੱਗਰੀ ਨੂੰ ਹਟਾਉਣ ਦੀ ਦਰ ਸਥਿਰ ਹੈ, ਆਮ ਤੌਰ 'ਤੇ 0.8–1.2 μm/ਮਿੰਟ ਤੱਕ ਪਹੁੰਚਦੀ ਹੈ। ਹਾਲਾਂਕਿ, ਨਤੀਜੇ ਵਜੋਂ ਵੇਫਰ ਸਤਹ ਮੁਕਾਬਲਤਨ ਉੱਚ ਖੁਰਦਰੀ ਦੇ ਨਾਲ ਮੈਟ ਹੁੰਦੀ ਹੈ - ਆਮ ਤੌਰ 'ਤੇ ਲਗਭਗ 50 nm - ਜੋ ਬਾਅਦ ਦੇ ਪਾਲਿਸ਼ਿੰਗ ਕਦਮਾਂ 'ਤੇ ਉੱਚ ਮੰਗਾਂ ਲਗਾਉਂਦੀ ਹੈ।

2.2 ਸਿੰਗਲ-ਸਾਈਡ ਪੀਸਣਾ

ਇੱਕ-ਪਾਸੜ ਪੀਸਣ ਨਾਲ ਇੱਕ ਸਮੇਂ ਵਿੱਚ ਵੇਫਰ ਦੇ ਸਿਰਫ਼ ਇੱਕ ਪਾਸੇ ਦੀ ਪ੍ਰਕਿਰਿਆ ਹੁੰਦੀ ਹੈ। ਇਸ ਪ੍ਰਕਿਰਿਆ ਦੌਰਾਨ, ਵੇਫਰ ਨੂੰ ਇੱਕ ਸਟੀਲ ਪਲੇਟ 'ਤੇ ਮੋਮ ਨਾਲ ਲਗਾਇਆ ਜਾਂਦਾ ਹੈ। ਲਾਗੂ ਦਬਾਅ ਹੇਠ, ਸਬਸਟਰੇਟ ਥੋੜ੍ਹਾ ਜਿਹਾ ਵਿਗਾੜ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਉੱਪਰਲੀ ਸਤ੍ਹਾ ਸਮਤਲ ਹੋ ਜਾਂਦੀ ਹੈ। ਪੀਸਣ ਤੋਂ ਬਾਅਦ, ਹੇਠਲੀ ਸਤ੍ਹਾ ਨੂੰ ਸਮਤਲ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਜਦੋਂ ਦਬਾਅ ਹਟਾ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ, ਤਾਂ ਉੱਪਰਲੀ ਸਤ੍ਹਾ ਆਪਣੇ ਅਸਲੀ ਆਕਾਰ ਵਿੱਚ ਮੁੜ ਪ੍ਰਾਪਤ ਕਰਨ ਦੀ ਕੋਸ਼ਿਸ਼ ਕਰਦੀ ਹੈ, ਜੋ ਪਹਿਲਾਂ ਤੋਂ ਜ਼ਮੀਨੀ ਹੇਠਲੀ ਸਤ੍ਹਾ ਨੂੰ ਵੀ ਪ੍ਰਭਾਵਿਤ ਕਰਦੀ ਹੈ - ਜਿਸ ਨਾਲ ਦੋਵੇਂ ਪਾਸੇ ਵਿਗੜ ਜਾਂਦੇ ਹਨ ਅਤੇ ਸਮਤਲਤਾ ਵਿੱਚ ਗਿਰਾਵਟ ਆਉਂਦੀ ਹੈ।

ਇਸ ਤੋਂ ਇਲਾਵਾ, ਪੀਸਣ ਵਾਲੀ ਪਲੇਟ ਥੋੜ੍ਹੇ ਸਮੇਂ ਵਿੱਚ ਅਵਤਲ ਬਣ ਸਕਦੀ ਹੈ, ਜਿਸ ਕਾਰਨ ਵੇਫਰ ਉੱਤਲ ਬਣ ਜਾਂਦਾ ਹੈ। ਪਲੇਟ ਦੀ ਸਮਤਲਤਾ ਬਣਾਈ ਰੱਖਣ ਲਈ, ਵਾਰ-ਵਾਰ ਡ੍ਰੈਸਿੰਗ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਘੱਟ ਕੁਸ਼ਲਤਾ ਅਤੇ ਮਾੜੀ ਵੇਫਰ ਸਮਤਲਤਾ ਦੇ ਕਾਰਨ, ਇੱਕ-ਪਾਸੜ ਪੀਸਣਾ ਵੱਡੇ ਪੱਧਰ 'ਤੇ ਉਤਪਾਦਨ ਲਈ ਢੁਕਵਾਂ ਨਹੀਂ ਹੈ।

ਆਮ ਤੌਰ 'ਤੇ, #8000 ਪੀਸਣ ਵਾਲੇ ਪਹੀਏ ਬਾਰੀਕ ਪੀਸਣ ਲਈ ਵਰਤੇ ਜਾਂਦੇ ਹਨ। ਜਪਾਨ ਵਿੱਚ, ਇਹ ਪ੍ਰਕਿਰਿਆ ਮੁਕਾਬਲਤਨ ਪਰਿਪੱਕ ਹੈ ਅਤੇ ਇੱਥੋਂ ਤੱਕ ਕਿ #30000 ਪਾਲਿਸ਼ਿੰਗ ਪਹੀਆਂ ਦੀ ਵਰਤੋਂ ਵੀ ਕਰਦੀ ਹੈ। ਇਹ ਪ੍ਰੋਸੈਸ ਕੀਤੇ ਵੇਫਰਾਂ ਦੀ ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ 2 nm ਤੋਂ ਹੇਠਾਂ ਪਹੁੰਚਣ ਦੀ ਆਗਿਆ ਦਿੰਦਾ ਹੈ, ਜਿਸ ਨਾਲ ਵੇਫਰਾਂ ਨੂੰ ਵਾਧੂ ਪ੍ਰੋਸੈਸਿੰਗ ਤੋਂ ਬਿਨਾਂ ਅੰਤਿਮ CMP (ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ) ਲਈ ਤਿਆਰ ਕੀਤਾ ਜਾਂਦਾ ਹੈ।

2.3 ਸਿੰਗਲ-ਸਾਈਡ ਥਿਨਿੰਗ ਤਕਨਾਲੋਜੀ

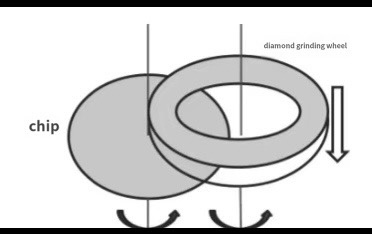

ਡਾਇਮੰਡ ਸਿੰਗਲ-ਸਾਈਡ ਥਿਨਿੰਗ ਤਕਨਾਲੋਜੀ ਸਿੰਗਲ-ਸਾਈਡ ਪੀਸਣ ਦਾ ਇੱਕ ਨਵਾਂ ਤਰੀਕਾ ਹੈ। ਜਿਵੇਂ ਕਿ ਚਿੱਤਰ 5 ਵਿੱਚ ਦਰਸਾਇਆ ਗਿਆ ਹੈ (ਇੱਥੇ ਨਹੀਂ ਦਿਖਾਇਆ ਗਿਆ), ਪ੍ਰਕਿਰਿਆ ਇੱਕ ਹੀਰਾ-ਬੰਧਿਤ ਪੀਸਣ ਵਾਲੀ ਪਲੇਟ ਦੀ ਵਰਤੋਂ ਕਰਦੀ ਹੈ। ਵੇਫਰ ਨੂੰ ਵੈਕਿਊਮ ਸੋਖਣ ਦੁਆਰਾ ਸਥਿਰ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਜਦੋਂ ਕਿ ਵੇਫਰ ਅਤੇ ਹੀਰਾ ਪੀਸਣ ਵਾਲਾ ਪਹੀਆ ਦੋਵੇਂ ਇੱਕੋ ਸਮੇਂ ਘੁੰਮਦੇ ਹਨ। ਪੀਸਣ ਵਾਲਾ ਪਹੀਆ ਹੌਲੀ-ਹੌਲੀ ਹੇਠਾਂ ਵੱਲ ਵਧਦਾ ਹੈ ਤਾਂ ਜੋ ਵੇਫਰ ਨੂੰ ਇੱਕ ਨਿਸ਼ਾਨਾ ਮੋਟਾਈ ਤੱਕ ਪਤਲਾ ਕੀਤਾ ਜਾ ਸਕੇ। ਇੱਕ ਪਾਸੇ ਦੇ ਪੂਰਾ ਹੋਣ ਤੋਂ ਬਾਅਦ, ਦੂਜੇ ਪਾਸੇ ਦੀ ਪ੍ਰਕਿਰਿਆ ਕਰਨ ਲਈ ਵੇਫਰ ਨੂੰ ਪਲਟ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ।

ਪਤਲਾ ਹੋਣ ਤੋਂ ਬਾਅਦ, 100 ਮਿਲੀਮੀਟਰ ਵੇਫਰ ਇਹ ਪ੍ਰਾਪਤ ਕਰ ਸਕਦਾ ਹੈ:

ਝੁਕਣਾ < 5 μm

ਟੀਟੀਵੀ < 2 μm

ਸਤ੍ਹਾ ਖੁਰਦਰੀ < 1 nm

ਇਹ ਸਿੰਗਲ-ਵੇਫਰ ਪ੍ਰੋਸੈਸਿੰਗ ਵਿਧੀ ਉੱਚ ਸਥਿਰਤਾ, ਸ਼ਾਨਦਾਰ ਇਕਸਾਰਤਾ, ਅਤੇ ਉੱਚ ਸਮੱਗਰੀ ਹਟਾਉਣ ਦੀ ਦਰ ਪ੍ਰਦਾਨ ਕਰਦੀ ਹੈ। ਰਵਾਇਤੀ ਦੋ-ਪਾਸੜ ਪੀਸਣ ਦੇ ਮੁਕਾਬਲੇ, ਇਹ ਤਕਨੀਕ ਪੀਸਣ ਦੀ ਕੁਸ਼ਲਤਾ ਵਿੱਚ 50% ਤੋਂ ਵੱਧ ਸੁਧਾਰ ਕਰਦੀ ਹੈ।

2.4 ਦੋ-ਪਾਸੜ ਪੀਸਣਾ

ਦੋ-ਪਾਸੜ ਪੀਸਣ ਲਈ ਸਬਸਟਰੇਟ ਦੇ ਦੋਵਾਂ ਪਾਸਿਆਂ ਨੂੰ ਇੱਕੋ ਸਮੇਂ ਪੀਸਣ ਲਈ ਉੱਪਰਲੀ ਅਤੇ ਹੇਠਲੀ ਪੀਸਣ ਵਾਲੀ ਪਲੇਟ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਜਿਸ ਨਾਲ ਦੋਵਾਂ ਪਾਸਿਆਂ ਦੀ ਸਤ੍ਹਾ ਦੀ ਸ਼ਾਨਦਾਰ ਗੁਣਵੱਤਾ ਯਕੀਨੀ ਬਣਾਈ ਜਾਂਦੀ ਹੈ।

ਇਸ ਪ੍ਰਕਿਰਿਆ ਦੌਰਾਨ, ਪੀਸਣ ਵਾਲੀਆਂ ਪਲੇਟਾਂ ਪਹਿਲਾਂ ਵਰਕਪੀਸ ਦੇ ਸਭ ਤੋਂ ਉੱਚੇ ਬਿੰਦੂਆਂ 'ਤੇ ਦਬਾਅ ਪਾਉਂਦੀਆਂ ਹਨ, ਜਿਸ ਨਾਲ ਵਿਗਾੜ ਹੁੰਦਾ ਹੈ ਅਤੇ ਉਨ੍ਹਾਂ ਬਿੰਦੂਆਂ 'ਤੇ ਸਮੱਗਰੀ ਹੌਲੀ-ਹੌਲੀ ਹਟਾਈ ਜਾਂਦੀ ਹੈ। ਜਿਵੇਂ-ਜਿਵੇਂ ਉੱਚੇ ਸਥਾਨਾਂ ਨੂੰ ਪੱਧਰਾ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਸਬਸਟਰੇਟ 'ਤੇ ਦਬਾਅ ਹੌਲੀ-ਹੌਲੀ ਹੋਰ ਇਕਸਾਰ ਹੋ ਜਾਂਦਾ ਹੈ, ਜਿਸਦੇ ਨਤੀਜੇ ਵਜੋਂ ਪੂਰੀ ਸਤ੍ਹਾ 'ਤੇ ਇਕਸਾਰ ਵਿਕਾਰ ਹੁੰਦਾ ਹੈ। ਇਹ ਉੱਪਰਲੀਆਂ ਅਤੇ ਹੇਠਲੀਆਂ ਦੋਵਾਂ ਸਤਹਾਂ ਨੂੰ ਬਰਾਬਰ ਜ਼ਮੀਨ 'ਤੇ ਰੱਖਣ ਦੀ ਆਗਿਆ ਦਿੰਦਾ ਹੈ। ਇੱਕ ਵਾਰ ਪੀਸਣ ਪੂਰਾ ਹੋ ਜਾਣ 'ਤੇ ਅਤੇ ਦਬਾਅ ਛੱਡ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ, ਸਬਸਟਰੇਟ ਦਾ ਹਰੇਕ ਹਿੱਸਾ ਉਸ ਦੇ ਅਨੁਭਵ ਕੀਤੇ ਗਏ ਬਰਾਬਰ ਦਬਾਅ ਦੇ ਕਾਰਨ ਇਕਸਾਰ ਠੀਕ ਹੋ ਜਾਂਦਾ ਹੈ। ਇਸ ਨਾਲ ਘੱਟੋ-ਘੱਟ ਵਾਰਪਿੰਗ ਅਤੇ ਚੰਗੀ ਸਮਤਲਤਾ ਹੁੰਦੀ ਹੈ।

ਪੀਸਣ ਤੋਂ ਬਾਅਦ ਵੇਫਰ ਦੀ ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ ਘਸਾਉਣ ਵਾਲੇ ਕਣ ਦੇ ਆਕਾਰ 'ਤੇ ਨਿਰਭਰ ਕਰਦੀ ਹੈ—ਛੋਟੇ ਕਣ ਨਿਰਵਿਘਨ ਸਤਹਾਂ ਪੈਦਾ ਕਰਦੇ ਹਨ। ਦੋ-ਪਾਸੜ ਪੀਸਣ ਲਈ 5 μm ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਸਮੇਂ, ਵੇਫਰ ਸਮਤਲਤਾ ਅਤੇ ਮੋਟਾਈ ਭਿੰਨਤਾ ਨੂੰ 5 μm ਦੇ ਅੰਦਰ ਨਿਯੰਤਰਿਤ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ। ਐਟੋਮਿਕ ਫੋਰਸ ਮਾਈਕ੍ਰੋਸਕੋਪੀ (AFM) ਮਾਪ ਲਗਭਗ 100 nm ਦੀ ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ (Rq) ਦਿਖਾਉਂਦੇ ਹਨ, ਜਿਸ ਵਿੱਚ 380 nm ਤੱਕ ਡੂੰਘੇ ਪੀਸਣ ਵਾਲੇ ਟੋਏ ਹੁੰਦੇ ਹਨ ਅਤੇ ਘਸਾਉਣ ਵਾਲੀ ਕਿਰਿਆ ਕਾਰਨ ਦਿਖਾਈ ਦੇਣ ਵਾਲੇ ਰੇਖਿਕ ਨਿਸ਼ਾਨ ਹੁੰਦੇ ਹਨ।

ਇੱਕ ਹੋਰ ਉੱਨਤ ਵਿਧੀ ਵਿੱਚ ਪੌਲੀਕ੍ਰਿਸਟਲਾਈਨ ਡਾਇਮੰਡ ਸਲਰੀ ਦੇ ਨਾਲ ਮਿਲ ਕੇ ਪੌਲੀਯੂਰੀਥੇਨ ਫੋਮ ਪੈਡਾਂ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਦੋ-ਪਾਸੜ ਪੀਸਣਾ ਸ਼ਾਮਲ ਹੈ। ਇਹ ਪ੍ਰਕਿਰਿਆ ਬਹੁਤ ਘੱਟ ਸਤਹ ਖੁਰਦਰੀ ਵਾਲੇ ਵੇਫਰ ਪੈਦਾ ਕਰਦੀ ਹੈ, ਜੋ Ra < 3 nm ਪ੍ਰਾਪਤ ਕਰਦੀ ਹੈ, ਜੋ ਕਿ SiC ਸਬਸਟਰੇਟਾਂ ਦੀ ਬਾਅਦ ਵਿੱਚ ਪਾਲਿਸ਼ਿੰਗ ਲਈ ਬਹੁਤ ਲਾਭਦਾਇਕ ਹੈ।

ਹਾਲਾਂਕਿ, ਸਤ੍ਹਾ ਖੁਰਚਣਾ ਇੱਕ ਅਣਸੁਲਝਿਆ ਮੁੱਦਾ ਬਣਿਆ ਹੋਇਆ ਹੈ। ਇਸ ਤੋਂ ਇਲਾਵਾ, ਇਸ ਪ੍ਰਕਿਰਿਆ ਵਿੱਚ ਵਰਤਿਆ ਜਾਣ ਵਾਲਾ ਪੌਲੀਕ੍ਰਿਸਟਲਾਈਨ ਹੀਰਾ ਵਿਸਫੋਟਕ ਸੰਸਲੇਸ਼ਣ ਦੁਆਰਾ ਤਿਆਰ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਜੋ ਕਿ ਤਕਨੀਕੀ ਤੌਰ 'ਤੇ ਚੁਣੌਤੀਪੂਰਨ ਹੈ, ਘੱਟ ਮਾਤਰਾ ਵਿੱਚ ਪੈਦਾ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਬਹੁਤ ਮਹਿੰਗਾ ਹੈ।

SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਦੀ ਪਾਲਿਸ਼ਿੰਗ

ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ (SiC) ਵੇਫਰਾਂ 'ਤੇ ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੀ ਪਾਲਿਸ਼ ਕੀਤੀ ਸਤ੍ਹਾ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ, ਪਾਲਿਸ਼ ਕਰਨ ਲਈ ਪੀਸਣ ਵਾਲੇ ਟੋਏ ਅਤੇ ਨੈਨੋਮੀਟਰ-ਸਕੇਲ ਸਤ੍ਹਾ ਦੇ ਝੁਕਾਅ ਨੂੰ ਪੂਰੀ ਤਰ੍ਹਾਂ ਹਟਾਉਣਾ ਚਾਹੀਦਾ ਹੈ। ਟੀਚਾ ਇੱਕ ਨਿਰਵਿਘਨ, ਨੁਕਸ-ਮੁਕਤ ਸਤ੍ਹਾ ਪੈਦਾ ਕਰਨਾ ਹੈ ਜਿਸ ਵਿੱਚ ਕੋਈ ਗੰਦਗੀ ਜਾਂ ਗਿਰਾਵਟ ਨਹੀਂ ਹੋਵੇਗੀ, ਕੋਈ ਉਪ-ਸਤਹ ਨੂੰ ਨੁਕਸਾਨ ਨਹੀਂ ਹੋਵੇਗਾ, ਅਤੇ ਕੋਈ ਬਚਿਆ ਹੋਇਆ ਸਤਹ ਤਣਾਅ ਨਹੀਂ ਹੋਵੇਗਾ।

3.1 SiC ਵੇਫਰਾਂ ਦੀ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ ਅਤੇ CMP

ਇੱਕ SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਇੰਗੋਟ ਦੇ ਵਾਧੇ ਤੋਂ ਬਾਅਦ, ਸਤ੍ਹਾ ਦੇ ਨੁਕਸ ਇਸਨੂੰ ਐਪੀਟੈਕਸੀਅਲ ਵਾਧੇ ਲਈ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਵਰਤੇ ਜਾਣ ਤੋਂ ਰੋਕਦੇ ਹਨ। ਇਸ ਲਈ, ਹੋਰ ਪ੍ਰਕਿਰਿਆ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਇੰਗੋਟ ਨੂੰ ਪਹਿਲਾਂ ਗੋਲ ਕਰਕੇ ਇੱਕ ਮਿਆਰੀ ਸਿਲੰਡਰ ਰੂਪ ਵਿੱਚ ਆਕਾਰ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ, ਫਿਰ ਤਾਰ ਕੱਟਣ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਵੇਫਰਾਂ ਵਿੱਚ ਕੱਟਿਆ ਜਾਂਦਾ ਹੈ, ਉਸ ਤੋਂ ਬਾਅਦ ਕ੍ਰਿਸਟਲੋਗ੍ਰਾਫਿਕ ਓਰੀਐਂਟੇਸ਼ਨ ਵੈਰੀਫਿਕੇਸ਼ਨ ਹੁੰਦਾ ਹੈ। ਪਾਲਿਸ਼ਿੰਗ ਵੇਫਰ ਦੀ ਗੁਣਵੱਤਾ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ, ਕ੍ਰਿਸਟਲ ਵਾਧੇ ਦੇ ਨੁਕਸ ਅਤੇ ਪਹਿਲਾਂ ਦੇ ਪ੍ਰੋਸੈਸਿੰਗ ਕਦਮਾਂ ਕਾਰਨ ਹੋਣ ਵਾਲੇ ਸੰਭਾਵੀ ਸਤ੍ਹਾ ਦੇ ਨੁਕਸਾਨ ਨੂੰ ਹੱਲ ਕਰਨ ਲਈ ਇੱਕ ਮਹੱਤਵਪੂਰਨ ਕਦਮ ਹੈ।

SiC 'ਤੇ ਸਤ੍ਹਾ ਦੇ ਨੁਕਸਾਨ ਦੀਆਂ ਪਰਤਾਂ ਨੂੰ ਹਟਾਉਣ ਲਈ ਚਾਰ ਮੁੱਖ ਤਰੀਕੇ ਹਨ:

ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ: ਸਧਾਰਨ ਪਰ ਝਰੀਟਾਂ ਛੱਡਦਾ ਹੈ; ਸ਼ੁਰੂਆਤੀ ਪਾਲਿਸ਼ਿੰਗ ਲਈ ਢੁਕਵਾਂ।

ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ (CMP): ਕੈਮੀਕਲ ਐਚਿੰਗ ਰਾਹੀਂ ਖੁਰਚਿਆਂ ਨੂੰ ਹਟਾਉਂਦਾ ਹੈ; ਸ਼ੁੱਧਤਾ ਪਾਲਿਸ਼ਿੰਗ ਲਈ ਢੁਕਵਾਂ।

ਹਾਈਡ੍ਰੋਜਨ ਐਚਿੰਗ: ਗੁੰਝਲਦਾਰ ਉਪਕਰਣਾਂ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਜੋ ਆਮ ਤੌਰ 'ਤੇ HTCVD ਪ੍ਰਕਿਰਿਆਵਾਂ ਵਿੱਚ ਵਰਤੇ ਜਾਂਦੇ ਹਨ।

ਪਲਾਜ਼ਮਾ-ਸਹਾਇਤਾ ਪ੍ਰਾਪਤ ਪਾਲਿਸ਼ਿੰਗ: ਗੁੰਝਲਦਾਰ ਅਤੇ ਬਹੁਤ ਘੱਟ ਵਰਤੀ ਜਾਂਦੀ ਹੈ।

ਸਿਰਫ਼ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ ਨਾਲ ਖੁਰਚਣ ਦਾ ਕਾਰਨ ਬਣਦਾ ਹੈ, ਜਦੋਂ ਕਿ ਸਿਰਫ਼ ਰਸਾਇਣਕ ਪਾਲਿਸ਼ਿੰਗ ਨਾਲ ਅਸਮਾਨ ਐਚਿੰਗ ਹੋ ਸਕਦੀ ਹੈ। CMP ਦੋਵਾਂ ਫਾਇਦਿਆਂ ਨੂੰ ਜੋੜਦਾ ਹੈ ਅਤੇ ਇੱਕ ਕੁਸ਼ਲ, ਲਾਗਤ-ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਹੱਲ ਪੇਸ਼ ਕਰਦਾ ਹੈ।

CMP ਕਾਰਜਸ਼ੀਲ ਸਿਧਾਂਤ

CMP ਇੱਕ ਘੁੰਮਦੇ ਪਾਲਿਸ਼ਿੰਗ ਪੈਡ ਦੇ ਵਿਰੁੱਧ ਇੱਕ ਸੈੱਟ ਦਬਾਅ ਹੇਠ ਵੇਫਰ ਨੂੰ ਘੁੰਮਾ ਕੇ ਕੰਮ ਕਰਦਾ ਹੈ। ਇਹ ਸਾਪੇਖਿਕ ਗਤੀ, ਸਲਰੀ ਵਿੱਚ ਨੈਨੋ-ਆਕਾਰ ਦੇ ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਤੋਂ ਮਕੈਨੀਕਲ ਘਸਾਉਣ ਅਤੇ ਪ੍ਰਤੀਕਿਰਿਆਸ਼ੀਲ ਏਜੰਟਾਂ ਦੀ ਰਸਾਇਣਕ ਕਿਰਿਆ ਦੇ ਨਾਲ, ਸਤਹ ਦੇ ਯੋਜਨਾਕਰਨ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਦੀ ਹੈ।

ਵਰਤੀ ਗਈ ਮੁੱਖ ਸਮੱਗਰੀ:

ਪਾਲਿਸ਼ਿੰਗ ਸਲਰੀ: ਇਸ ਵਿੱਚ ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥ ਅਤੇ ਰਸਾਇਣਕ ਰੀਐਜੈਂਟ ਹੁੰਦੇ ਹਨ।

ਪਾਲਿਸ਼ਿੰਗ ਪੈਡ: ਵਰਤੋਂ ਦੌਰਾਨ ਘਿਸ ਜਾਂਦਾ ਹੈ, ਜਿਸ ਨਾਲ ਪੋਰ ਦਾ ਆਕਾਰ ਘਟ ਜਾਂਦਾ ਹੈ ਅਤੇ ਸਲਰੀ ਡਿਲੀਵਰੀ ਕੁਸ਼ਲਤਾ ਘਟ ਜਾਂਦੀ ਹੈ। ਖੁਰਦਰਾਪਨ ਨੂੰ ਬਹਾਲ ਕਰਨ ਲਈ ਨਿਯਮਤ ਡ੍ਰੈਸਿੰਗ, ਆਮ ਤੌਰ 'ਤੇ ਡਾਇਮੰਡ ਡ੍ਰੈਸਰ ਦੀ ਵਰਤੋਂ ਕਰਕੇ, ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ।

ਆਮ CMP ਪ੍ਰਕਿਰਿਆ

ਘਸਾਉਣ ਵਾਲਾ: 0.5 μm ਹੀਰਾ ਸਲਰੀ

ਨਿਸ਼ਾਨਾ ਸਤਹ ਖੁਰਦਰੀ: ~0.7 nm

ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ:

ਪਾਲਿਸ਼ਿੰਗ ਉਪਕਰਣ: AP-810 ਸਿੰਗਲ-ਸਾਈਡ ਪਾਲਿਸ਼ਰ

ਦਬਾਅ: 200 ਗ੍ਰਾਮ/ਸੈ.ਮੀ.²

ਪਲੇਟ ਦੀ ਗਤੀ: 50 ਆਰਪੀਐਮ

ਸਿਰੇਮਿਕ ਹੋਲਡਰ ਸਪੀਡ: 38 ਆਰਪੀਐਮ

ਸਲਰੀ ਰਚਨਾ:

SiO₂ (30 wt%, pH = 10.15)

0–70 wt% H₂O₂ (30 wt%, ਰੀਐਜੈਂਟ ਗ੍ਰੇਡ)

5 wt% KOH ਅਤੇ 1 wt% HNO₃ ਦੀ ਵਰਤੋਂ ਕਰਕੇ pH ਨੂੰ 8.5 'ਤੇ ਐਡਜਸਟ ਕਰੋ।

ਸਲਰੀ ਵਹਾਅ ਦਰ: 3 ਲੀਟਰ/ਮਿੰਟ, ਰੀਸਰਕੁਲੇਟਿਡ

ਇਹ ਪ੍ਰਕਿਰਿਆ ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਢੰਗ ਨਾਲ SiC ਵੇਫਰ ਦੀ ਗੁਣਵੱਤਾ ਵਿੱਚ ਸੁਧਾਰ ਕਰਦੀ ਹੈ ਅਤੇ ਡਾਊਨਸਟ੍ਰੀਮ ਪ੍ਰਕਿਰਿਆਵਾਂ ਲਈ ਜ਼ਰੂਰਤਾਂ ਨੂੰ ਪੂਰਾ ਕਰਦੀ ਹੈ।

ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ ਵਿੱਚ ਤਕਨੀਕੀ ਚੁਣੌਤੀਆਂ

SiC, ਇੱਕ ਵਿਸ਼ਾਲ ਬੈਂਡਗੈਪ ਸੈਮੀਕੰਡਕਟਰ ਦੇ ਰੂਪ ਵਿੱਚ, ਇਲੈਕਟ੍ਰਾਨਿਕਸ ਉਦਯੋਗ ਵਿੱਚ ਇੱਕ ਮਹੱਤਵਪੂਰਨ ਭੂਮਿਕਾ ਨਿਭਾਉਂਦਾ ਹੈ। ਸ਼ਾਨਦਾਰ ਭੌਤਿਕ ਅਤੇ ਰਸਾਇਣਕ ਗੁਣਾਂ ਦੇ ਨਾਲ, SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਬਹੁਤ ਜ਼ਿਆਦਾ ਵਾਤਾਵਰਣਾਂ, ਜਿਵੇਂ ਕਿ ਉੱਚ ਤਾਪਮਾਨ, ਉੱਚ ਆਵਿਰਤੀ, ਉੱਚ ਸ਼ਕਤੀ, ਅਤੇ ਰੇਡੀਏਸ਼ਨ ਪ੍ਰਤੀਰੋਧ ਲਈ ਅਨੁਕੂਲ ਹਨ। ਹਾਲਾਂਕਿ, ਇਸਦਾ ਸਖ਼ਤ ਅਤੇ ਭੁਰਭੁਰਾ ਸੁਭਾਅ ਪੀਸਣ ਅਤੇ ਪਾਲਿਸ਼ ਕਰਨ ਲਈ ਵੱਡੀਆਂ ਚੁਣੌਤੀਆਂ ਪੇਸ਼ ਕਰਦਾ ਹੈ।

ਜਿਵੇਂ ਕਿ ਪ੍ਰਮੁੱਖ ਵਿਸ਼ਵਵਿਆਪੀ ਨਿਰਮਾਤਾ 6-ਇੰਚ ਤੋਂ 8-ਇੰਚ ਵੇਫਰਾਂ ਵਿੱਚ ਤਬਦੀਲੀ ਕਰ ਰਹੇ ਹਨ, ਪ੍ਰੋਸੈਸਿੰਗ ਦੌਰਾਨ ਕ੍ਰੈਕਿੰਗ ਅਤੇ ਵੇਫਰ ਨੂੰ ਨੁਕਸਾਨ ਵਰਗੇ ਮੁੱਦੇ ਵਧੇਰੇ ਪ੍ਰਮੁੱਖ ਹੋ ਗਏ ਹਨ, ਜੋ ਉਪਜ ਨੂੰ ਮਹੱਤਵਪੂਰਨ ਤੌਰ 'ਤੇ ਪ੍ਰਭਾਵਿਤ ਕਰ ਰਹੇ ਹਨ। 8-ਇੰਚ SiC ਸਬਸਟਰੇਟਾਂ ਦੀਆਂ ਤਕਨੀਕੀ ਚੁਣੌਤੀਆਂ ਨੂੰ ਹੱਲ ਕਰਨਾ ਹੁਣ ਉਦਯੋਗ ਦੀ ਤਰੱਕੀ ਲਈ ਇੱਕ ਮੁੱਖ ਮਾਪਦੰਡ ਹੈ।

8-ਇੰਚ ਯੁੱਗ ਵਿੱਚ, SiC ਵੇਫਰ ਪ੍ਰੋਸੈਸਿੰਗ ਨੂੰ ਕਈ ਚੁਣੌਤੀਆਂ ਦਾ ਸਾਹਮਣਾ ਕਰਨਾ ਪੈਂਦਾ ਹੈ:

ਪ੍ਰਤੀ ਬੈਚ ਚਿੱਪ ਆਉਟਪੁੱਟ ਵਧਾਉਣ, ਕਿਨਾਰੇ ਦੇ ਨੁਕਸਾਨ ਨੂੰ ਘਟਾਉਣ ਅਤੇ ਉਤਪਾਦਨ ਲਾਗਤਾਂ ਨੂੰ ਘਟਾਉਣ ਲਈ ਵੇਫਰ ਸਕੇਲਿੰਗ ਜ਼ਰੂਰੀ ਹੈ - ਖਾਸ ਕਰਕੇ ਇਲੈਕਟ੍ਰਿਕ ਵਾਹਨ ਐਪਲੀਕੇਸ਼ਨਾਂ ਵਿੱਚ ਵੱਧ ਰਹੀ ਮੰਗ ਨੂੰ ਦੇਖਦੇ ਹੋਏ।

ਜਦੋਂ ਕਿ 8-ਇੰਚ SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਦਾ ਵਾਧਾ ਪਰਿਪੱਕ ਹੋ ਗਿਆ ਹੈ, ਪੀਸਣ ਅਤੇ ਪਾਲਿਸ਼ ਕਰਨ ਵਰਗੀਆਂ ਬੈਕ-ਐਂਡ ਪ੍ਰਕਿਰਿਆਵਾਂ ਅਜੇ ਵੀ ਰੁਕਾਵਟਾਂ ਦਾ ਸਾਹਮਣਾ ਕਰਦੀਆਂ ਹਨ, ਨਤੀਜੇ ਵਜੋਂ ਘੱਟ ਪੈਦਾਵਾਰ (ਸਿਰਫ 40-50%) ਹੁੰਦੀ ਹੈ।

ਵੱਡੇ ਵੇਫਰਾਂ ਵਿੱਚ ਵਧੇਰੇ ਗੁੰਝਲਦਾਰ ਦਬਾਅ ਵੰਡ ਹੁੰਦੀ ਹੈ, ਜਿਸ ਨਾਲ ਪਾਲਿਸ਼ਿੰਗ ਤਣਾਅ ਅਤੇ ਉਪਜ ਦੀ ਇਕਸਾਰਤਾ ਦੇ ਪ੍ਰਬੰਧਨ ਵਿੱਚ ਮੁਸ਼ਕਲ ਵਧ ਜਾਂਦੀ ਹੈ।

ਹਾਲਾਂਕਿ 8-ਇੰਚ ਵੇਫਰਾਂ ਦੀ ਮੋਟਾਈ 6-ਇੰਚ ਵੇਫਰਾਂ ਦੇ ਨੇੜੇ ਆ ਰਹੀ ਹੈ, ਪਰ ਤਣਾਅ ਅਤੇ ਵਾਰਪਿੰਗ ਦੇ ਕਾਰਨ ਹੈਂਡਲਿੰਗ ਦੌਰਾਨ ਉਹਨਾਂ ਨੂੰ ਨੁਕਸਾਨ ਹੋਣ ਦਾ ਖ਼ਤਰਾ ਵਧੇਰੇ ਹੁੰਦਾ ਹੈ।

ਕੱਟਣ ਨਾਲ ਸਬੰਧਤ ਤਣਾਅ, ਵਾਰਪੇਜ ਅਤੇ ਕ੍ਰੈਕਿੰਗ ਨੂੰ ਘਟਾਉਣ ਲਈ, ਲੇਜ਼ਰ ਕਟਿੰਗ ਦੀ ਵਰਤੋਂ ਵੱਧ ਤੋਂ ਵੱਧ ਕੀਤੀ ਜਾ ਰਹੀ ਹੈ। ਹਾਲਾਂਕਿ:

ਲੰਬੀ-ਤਰੰਗ-ਲੰਬਾਈ ਵਾਲੇ ਲੇਜ਼ਰ ਥਰਮਲ ਨੁਕਸਾਨ ਦਾ ਕਾਰਨ ਬਣਦੇ ਹਨ।

ਛੋਟੀ-ਤਰੰਗ-ਲੰਬਾਈ ਵਾਲੇ ਲੇਜ਼ਰ ਭਾਰੀ ਮਲਬਾ ਪੈਦਾ ਕਰਦੇ ਹਨ ਅਤੇ ਨੁਕਸਾਨ ਦੀ ਪਰਤ ਨੂੰ ਡੂੰਘਾ ਕਰਦੇ ਹਨ, ਜਿਸ ਨਾਲ ਪਾਲਿਸ਼ਿੰਗ ਦੀ ਗੁੰਝਲਤਾ ਵਧ ਜਾਂਦੀ ਹੈ।

SiC ਲਈ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ ਵਰਕਫਲੋ

ਆਮ ਪ੍ਰਕਿਰਿਆ ਪ੍ਰਵਾਹ ਵਿੱਚ ਸ਼ਾਮਲ ਹਨ:

ਦਿਸ਼ਾ ਕਟਿੰਗ

ਮੋਟਾ ਪੀਸਣਾ

ਬਾਰੀਕ ਪੀਸਣਾ

ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ

ਅੰਤਿਮ ਪੜਾਅ ਵਜੋਂ ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ (CMP)

ਸੀਐਮਪੀ ਵਿਧੀ ਦੀ ਚੋਣ, ਪ੍ਰਕਿਰਿਆ ਰੂਟ ਡਿਜ਼ਾਈਨ, ਅਤੇ ਪੈਰਾਮੀਟਰਾਂ ਦਾ ਅਨੁਕੂਲਨ ਮਹੱਤਵਪੂਰਨ ਹਨ। ਸੈਮੀਕੰਡਕਟਰ ਨਿਰਮਾਣ ਵਿੱਚ, ਸੀਐਮਪੀ ਅਤਿ-ਨਿਰਵਿਘਨ, ਨੁਕਸ-ਮੁਕਤ, ਅਤੇ ਨੁਕਸਾਨ-ਮੁਕਤ ਸਤਹਾਂ ਵਾਲੇ ਐਸਆਈਸੀ ਵੇਫਰਾਂ ਦੇ ਉਤਪਾਦਨ ਲਈ ਨਿਰਣਾਇਕ ਕਦਮ ਹੈ, ਜੋ ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੇ ਐਪੀਟੈਕਸੀਅਲ ਵਿਕਾਸ ਲਈ ਜ਼ਰੂਰੀ ਹਨ।

(a) ਕਰੂਸੀਬਲ ਤੋਂ SiC ਇੰਗੋਟ ਨੂੰ ਹਟਾਓ;

(ਅ) ਬਾਹਰੀ ਵਿਆਸ ਪੀਸਣ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਸ਼ੁਰੂਆਤੀ ਆਕਾਰ ਦਿਓ;

(c) ਅਲਾਈਨਮੈਂਟ ਫਲੈਟਾਂ ਜਾਂ ਨੌਚਾਂ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਕ੍ਰਿਸਟਲ ਸਥਿਤੀ ਦਾ ਪਤਾ ਲਗਾਓ;

(d) ਮਲਟੀ-ਵਾਇਰ ਸਾਇੰਗ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਇੰਗਟ ਨੂੰ ਪਤਲੇ ਵੇਫਰਾਂ ਵਿੱਚ ਕੱਟੋ;

(e) ਪੀਸਣ ਅਤੇ ਪਾਲਿਸ਼ ਕਰਨ ਦੇ ਕਦਮਾਂ ਰਾਹੀਂ ਸ਼ੀਸ਼ੇ ਵਰਗੀ ਸਤ੍ਹਾ ਨਿਰਵਿਘਨਤਾ ਪ੍ਰਾਪਤ ਕਰੋ।

ਪ੍ਰੋਸੈਸਿੰਗ ਪੜਾਵਾਂ ਦੀ ਲੜੀ ਨੂੰ ਪੂਰਾ ਕਰਨ ਤੋਂ ਬਾਅਦ, SiC ਵੇਫਰ ਦਾ ਬਾਹਰੀ ਕਿਨਾਰਾ ਅਕਸਰ ਤਿੱਖਾ ਹੋ ਜਾਂਦਾ ਹੈ, ਜੋ ਹੈਂਡਲਿੰਗ ਜਾਂ ਵਰਤੋਂ ਦੌਰਾਨ ਚਿਪਿੰਗ ਦਾ ਜੋਖਮ ਵਧਾਉਂਦਾ ਹੈ। ਅਜਿਹੀ ਨਾਜ਼ੁਕਤਾ ਤੋਂ ਬਚਣ ਲਈ, ਕਿਨਾਰੇ ਨੂੰ ਪੀਸਣ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ।

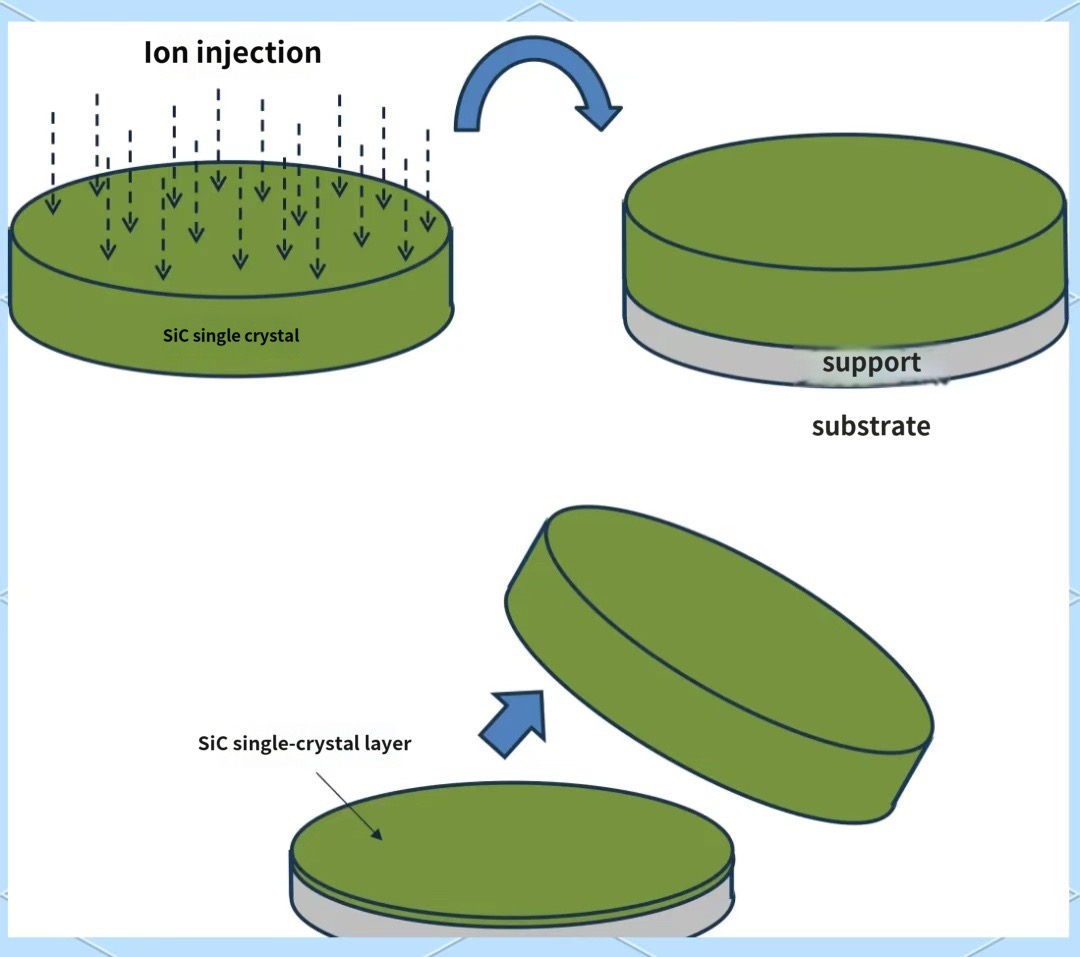

ਰਵਾਇਤੀ ਸਲਾਈਸਿੰਗ ਪ੍ਰਕਿਰਿਆਵਾਂ ਤੋਂ ਇਲਾਵਾ, SiC ਵੇਫਰ ਤਿਆਰ ਕਰਨ ਲਈ ਇੱਕ ਨਵੀਨਤਾਕਾਰੀ ਵਿਧੀ ਵਿੱਚ ਬੰਧਨ ਤਕਨਾਲੋਜੀ ਸ਼ਾਮਲ ਹੈ। ਇਹ ਪਹੁੰਚ ਇੱਕ ਪਤਲੀ SiC ਸਿੰਗਲ-ਕ੍ਰਿਸਟਲ ਪਰਤ ਨੂੰ ਇੱਕ ਵਿਭਿੰਨ ਸਬਸਟਰੇਟ (ਸਹਾਇਕ ਸਬਸਟਰੇਟ) ਨਾਲ ਜੋੜ ਕੇ ਵੇਫਰ ਫੈਬਰੀਕੇਸ਼ਨ ਨੂੰ ਸਮਰੱਥ ਬਣਾਉਂਦੀ ਹੈ।

ਚਿੱਤਰ 3 ਪ੍ਰਕਿਰਿਆ ਦੇ ਪ੍ਰਵਾਹ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ:

ਪਹਿਲਾਂ, ਹਾਈਡ੍ਰੋਜਨ ਆਇਨ ਇਮਪਲਾਂਟੇਸ਼ਨ ਜਾਂ ਸਮਾਨ ਤਕਨੀਕਾਂ ਰਾਹੀਂ SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਇੱਕ ਨਿਰਧਾਰਤ ਡੂੰਘਾਈ 'ਤੇ ਇੱਕ ਡੀਲੇਮੀਨੇਸ਼ਨ ਪਰਤ ਬਣਾਈ ਜਾਂਦੀ ਹੈ। ਪ੍ਰੋਸੈਸਡ SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਨੂੰ ਫਿਰ ਇੱਕ ਫਲੈਟ ਸਪੋਰਟਿੰਗ ਸਬਸਟਰੇਟ ਨਾਲ ਜੋੜਿਆ ਜਾਂਦਾ ਹੈ ਅਤੇ ਦਬਾਅ ਅਤੇ ਗਰਮੀ ਦੇ ਅਧੀਨ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਇਹ SiC ਸਿੰਗਲ-ਕ੍ਰਿਸਟਲ ਪਰਤ ਨੂੰ ਸਪੋਰਟਿੰਗ ਸਬਸਟਰੇਟ 'ਤੇ ਸਫਲ ਟ੍ਰਾਂਸਫਰ ਅਤੇ ਵੱਖ ਕਰਨ ਦੀ ਆਗਿਆ ਦਿੰਦਾ ਹੈ।

ਵੱਖ ਕੀਤੀ SiC ਪਰਤ ਲੋੜੀਂਦੀ ਸਮਤਲਤਾ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਸਤ੍ਹਾ ਦੇ ਇਲਾਜ ਵਿੱਚੋਂ ਗੁਜ਼ਰਦੀ ਹੈ ਅਤੇ ਇਸਨੂੰ ਬਾਅਦ ਦੀਆਂ ਬੰਧਨ ਪ੍ਰਕਿਰਿਆਵਾਂ ਵਿੱਚ ਦੁਬਾਰਾ ਵਰਤਿਆ ਜਾ ਸਕਦਾ ਹੈ। SiC ਕ੍ਰਿਸਟਲਾਂ ਦੇ ਰਵਾਇਤੀ ਕੱਟਣ ਦੇ ਮੁਕਾਬਲੇ, ਇਹ ਤਕਨੀਕ ਮਹਿੰਗੇ ਪਦਾਰਥਾਂ ਦੀ ਮੰਗ ਨੂੰ ਘਟਾਉਂਦੀ ਹੈ। ਹਾਲਾਂਕਿ ਤਕਨੀਕੀ ਚੁਣੌਤੀਆਂ ਅਜੇ ਵੀ ਹਨ, ਖੋਜ ਅਤੇ ਵਿਕਾਸ ਘੱਟ ਲਾਗਤ ਵਾਲੇ ਵੇਫਰ ਉਤਪਾਦਨ ਨੂੰ ਸਮਰੱਥ ਬਣਾਉਣ ਲਈ ਸਰਗਰਮੀ ਨਾਲ ਅੱਗੇ ਵਧ ਰਹੇ ਹਨ।

SiC ਦੀ ਉੱਚ ਕਠੋਰਤਾ ਅਤੇ ਰਸਾਇਣਕ ਸਥਿਰਤਾ ਨੂੰ ਦੇਖਦੇ ਹੋਏ - ਜੋ ਇਸਨੂੰ ਕਮਰੇ ਦੇ ਤਾਪਮਾਨ 'ਤੇ ਪ੍ਰਤੀਕ੍ਰਿਆਵਾਂ ਪ੍ਰਤੀ ਰੋਧਕ ਬਣਾਉਂਦੀ ਹੈ - ਬਾਰੀਕ ਪੀਸਣ ਵਾਲੇ ਟੋਇਆਂ ਨੂੰ ਹਟਾਉਣ, ਸਤ੍ਹਾ ਦੇ ਨੁਕਸਾਨ ਨੂੰ ਘਟਾਉਣ, ਖੁਰਚਿਆਂ, ਟੋਇਆਂ ਅਤੇ ਸੰਤਰੇ ਦੇ ਛਿਲਕੇ ਦੇ ਨੁਕਸ ਨੂੰ ਖਤਮ ਕਰਨ, ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ ਨੂੰ ਘਟਾਉਣ, ਸਮਤਲਤਾ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਅਤੇ ਸਤ੍ਹਾ ਦੀ ਗੁਣਵੱਤਾ ਨੂੰ ਵਧਾਉਣ ਲਈ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ।

ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੀ ਪਾਲਿਸ਼ ਕੀਤੀ ਸਤ੍ਹਾ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ, ਇਹ ਜ਼ਰੂਰੀ ਹੈ:

ਘ੍ਰਿਣਾਯੋਗ ਕਿਸਮਾਂ ਨੂੰ ਵਿਵਸਥਿਤ ਕਰੋ,

ਕਣਾਂ ਦਾ ਆਕਾਰ ਘਟਾਓ,

ਪ੍ਰਕਿਰਿਆ ਮਾਪਦੰਡਾਂ ਨੂੰ ਅਨੁਕੂਲ ਬਣਾਓ,

ਲੋੜੀਂਦੀ ਕਠੋਰਤਾ ਵਾਲੇ ਪਾਲਿਸ਼ਿੰਗ ਸਮੱਗਰੀ ਅਤੇ ਪੈਡ ਚੁਣੋ।

ਚਿੱਤਰ 7 ਦਰਸਾਉਂਦਾ ਹੈ ਕਿ 1 μm ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥਾਂ ਨਾਲ ਦੋ-ਪਾਸੜ ਪਾਲਿਸ਼ਿੰਗ 10 μm ਦੇ ਅੰਦਰ ਸਮਤਲਤਾ ਅਤੇ ਮੋਟਾਈ ਦੇ ਭਿੰਨਤਾ ਨੂੰ ਨਿਯੰਤਰਿਤ ਕਰ ਸਕਦੀ ਹੈ, ਅਤੇ ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ ਨੂੰ ਲਗਭਗ 0.25 nm ਤੱਕ ਘਟਾ ਸਕਦੀ ਹੈ।

3.2 ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ (CMP)

ਕੈਮੀਕਲ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ (CMP) ਰਸਾਇਣਕ ਐਚਿੰਗ ਦੇ ਨਾਲ ਅਲਟਰਾਫਾਈਨ ਪਾਰਟੀਕਲ ਐਬ੍ਰੇਸ਼ਨ ਨੂੰ ਜੋੜਦੀ ਹੈ ਤਾਂ ਜੋ ਪ੍ਰੋਸੈਸ ਕੀਤੀ ਜਾ ਰਹੀ ਸਮੱਗਰੀ 'ਤੇ ਇੱਕ ਨਿਰਵਿਘਨ, ਸਮਤਲ ਸਤਹ ਬਣਾਈ ਜਾ ਸਕੇ। ਮੂਲ ਸਿਧਾਂਤ ਇਹ ਹੈ:

ਪਾਲਿਸ਼ਿੰਗ ਸਲਰੀ ਅਤੇ ਵੇਫਰ ਸਤ੍ਹਾ ਦੇ ਵਿਚਕਾਰ ਇੱਕ ਰਸਾਇਣਕ ਪ੍ਰਤੀਕ੍ਰਿਆ ਹੁੰਦੀ ਹੈ, ਜਿਸ ਨਾਲ ਇੱਕ ਨਰਮ ਪਰਤ ਬਣ ਜਾਂਦੀ ਹੈ।

ਘਿਸਾਉਣ ਵਾਲੇ ਕਣਾਂ ਅਤੇ ਨਰਮ ਪਰਤ ਵਿਚਕਾਰ ਰਗੜ ਸਮੱਗਰੀ ਨੂੰ ਹਟਾ ਦਿੰਦੀ ਹੈ।

ਸੀਐਮਪੀ ਦੇ ਫਾਇਦੇ:

ਪੂਰੀ ਤਰ੍ਹਾਂ ਮਕੈਨੀਕਲ ਜਾਂ ਰਸਾਇਣਕ ਪਾਲਿਸ਼ਿੰਗ ਦੀਆਂ ਕਮੀਆਂ ਨੂੰ ਦੂਰ ਕਰਦਾ ਹੈ,

ਗਲੋਬਲ ਅਤੇ ਸਥਾਨਕ ਯੋਜਨਾਬੰਦੀ ਦੋਵਾਂ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਦਾ ਹੈ,

ਉੱਚ ਸਮਤਲਤਾ ਅਤੇ ਘੱਟ ਖੁਰਦਰੀ ਵਾਲੀਆਂ ਸਤਹਾਂ ਪੈਦਾ ਕਰਦਾ ਹੈ,

ਸਤ੍ਹਾ ਜਾਂ ਸਤ੍ਹਾ ਦੇ ਹੇਠਾਂ ਕੋਈ ਨੁਕਸਾਨ ਨਹੀਂ ਛੱਡਦਾ।

ਵਿਸਥਾਰ ਵਿੱਚ:

ਦਬਾਅ ਹੇਠ ਵੇਫਰ ਪਾਲਿਸ਼ਿੰਗ ਪੈਡ ਦੇ ਸਾਪੇਖਕ ਚਲਦਾ ਹੈ।

ਸਲਰੀ ਵਿੱਚ ਨੈਨੋਮੀਟਰ-ਸਕੇਲ ਘਸਾਉਣ ਵਾਲੇ ਪਦਾਰਥ (ਜਿਵੇਂ ਕਿ, SiO₂) ਸ਼ੀਅਰਿੰਗ, Si–C ਸਹਿ-ਸੰਯੋਜਕ ਬੰਧਨਾਂ ਨੂੰ ਕਮਜ਼ੋਰ ਕਰਨ ਅਤੇ ਸਮੱਗਰੀ ਨੂੰ ਹਟਾਉਣ ਨੂੰ ਵਧਾਉਣ ਵਿੱਚ ਹਿੱਸਾ ਲੈਂਦੇ ਹਨ।

ਸੀਐਮਪੀ ਤਕਨੀਕਾਂ ਦੀਆਂ ਕਿਸਮਾਂ:

ਮੁਫ਼ਤ ਘਸਾਉਣ ਵਾਲੀ ਪਾਲਿਸ਼ਿੰਗ: ਘਸਾਉਣ ਵਾਲੀਆਂ ਚੀਜ਼ਾਂ (ਜਿਵੇਂ ਕਿ, SiO₂) ਨੂੰ ਸਲਰੀ ਵਿੱਚ ਲਟਕਾਇਆ ਜਾਂਦਾ ਹੈ। ਸਮੱਗਰੀ ਨੂੰ ਹਟਾਉਣਾ ਤਿੰਨ-ਬਾਡੀ ਘਸਾਉਣ (ਵੇਫਰ-ਪੈਡ-ਘਸਾਉਣ ਵਾਲੀ) ਰਾਹੀਂ ਹੁੰਦਾ ਹੈ। ਇਕਸਾਰਤਾ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਲਈ ਘਸਾਉਣ ਵਾਲਾ ਆਕਾਰ (ਆਮ ਤੌਰ 'ਤੇ 60-200 nm), pH, ਅਤੇ ਤਾਪਮਾਨ ਨੂੰ ਸਹੀ ਢੰਗ ਨਾਲ ਨਿਯੰਤਰਿਤ ਕੀਤਾ ਜਾਣਾ ਚਾਹੀਦਾ ਹੈ।

ਸਥਿਰ ਘਸਾਉਣ ਵਾਲੀ ਪਾਲਿਸ਼ਿੰਗ: ਘਸਾਉਣ ਵਾਲੀਆਂ ਚੀਜ਼ਾਂ ਨੂੰ ਇਕੱਠਾ ਹੋਣ ਤੋਂ ਰੋਕਣ ਲਈ ਪਾਲਿਸ਼ਿੰਗ ਪੈਡ ਵਿੱਚ ਜੋੜਿਆ ਜਾਂਦਾ ਹੈ—ਉੱਚ-ਸ਼ੁੱਧਤਾ ਪ੍ਰਕਿਰਿਆ ਲਈ ਆਦਰਸ਼।

ਪਾਲਿਸ਼ਿੰਗ ਤੋਂ ਬਾਅਦ ਸਫਾਈ:

ਪਾਲਿਸ਼ ਕੀਤੇ ਵੇਫਰਾਂ ਵਿੱਚ ਇਹ ਸ਼ਾਮਲ ਹੁੰਦਾ ਹੈ:

ਰਸਾਇਣਕ ਸਫਾਈ (ਡੀਆਈ ਪਾਣੀ ਅਤੇ ਸਲਰੀ ਰਹਿੰਦ-ਖੂੰਹਦ ਨੂੰ ਹਟਾਉਣ ਸਮੇਤ),

DI ਪਾਣੀ ਨਾਲ ਕੁਰਲੀ ਕਰਨਾ, ਅਤੇ

ਗਰਮ ਨਾਈਟ੍ਰੋਜਨ ਸੁਕਾਉਣਾ

ਸਤ੍ਹਾ ਦੇ ਦੂਸ਼ਿਤ ਤੱਤਾਂ ਨੂੰ ਘੱਟ ਤੋਂ ਘੱਟ ਕਰਨ ਲਈ।

ਸਤ੍ਹਾ ਦੀ ਗੁਣਵੱਤਾ ਅਤੇ ਪ੍ਰਦਰਸ਼ਨ

ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ ਨੂੰ Ra < 0.3 nm ਤੱਕ ਘਟਾਇਆ ਜਾ ਸਕਦਾ ਹੈ, ਜੋ ਕਿ ਸੈਮੀਕੰਡਕਟਰ ਐਪੀਟੈਕਸੀ ਜ਼ਰੂਰਤਾਂ ਨੂੰ ਪੂਰਾ ਕਰਦਾ ਹੈ।

ਗਲੋਬਲ ਪਲੈਨਰਾਈਜ਼ੇਸ਼ਨ: ਰਸਾਇਣਕ ਨਰਮ ਕਰਨ ਅਤੇ ਮਕੈਨੀਕਲ ਹਟਾਉਣ ਦਾ ਸੁਮੇਲ ਖੁਰਚਿਆਂ ਅਤੇ ਅਸਮਾਨ ਐਚਿੰਗ ਨੂੰ ਘਟਾਉਂਦਾ ਹੈ, ਸ਼ੁੱਧ ਮਕੈਨੀਕਲ ਜਾਂ ਰਸਾਇਣਕ ਤਰੀਕਿਆਂ ਤੋਂ ਵੱਧ ਪ੍ਰਦਰਸ਼ਨ ਕਰਦਾ ਹੈ।

ਉੱਚ ਕੁਸ਼ਲਤਾ: SiC ਵਰਗੀਆਂ ਸਖ਼ਤ ਅਤੇ ਭੁਰਭੁਰਾ ਸਮੱਗਰੀਆਂ ਲਈ ਢੁਕਵਾਂ, ਜਿਸਦੀ ਸਮੱਗਰੀ ਹਟਾਉਣ ਦੀ ਦਰ 200 nm/h ਤੋਂ ਵੱਧ ਹੈ।

ਹੋਰ ਉੱਭਰ ਰਹੀਆਂ ਪਾਲਿਸ਼ਿੰਗ ਤਕਨੀਕਾਂ

CMP ਤੋਂ ਇਲਾਵਾ, ਵਿਕਲਪਿਕ ਤਰੀਕੇ ਪ੍ਰਸਤਾਵਿਤ ਕੀਤੇ ਗਏ ਹਨ, ਜਿਨ੍ਹਾਂ ਵਿੱਚ ਸ਼ਾਮਲ ਹਨ:

ਇਲੈਕਟ੍ਰੋਕੈਮੀਕਲ ਪਾਲਿਸ਼ਿੰਗ, ਕੈਟਾਲਿਸਟ-ਸਹਾਇਤਾ ਪ੍ਰਾਪਤ ਪਾਲਿਸ਼ਿੰਗ ਜਾਂ ਐਚਿੰਗ, ਅਤੇ

ਟ੍ਰਾਈਬੋਕੈਮੀਕਲ ਪਾਲਿਸ਼ਿੰਗ।

ਹਾਲਾਂਕਿ, ਇਹ ਤਰੀਕੇ ਅਜੇ ਵੀ ਖੋਜ ਦੇ ਪੜਾਅ ਵਿੱਚ ਹਨ ਅਤੇ SiC ਦੇ ਚੁਣੌਤੀਪੂਰਨ ਪਦਾਰਥਕ ਗੁਣਾਂ ਦੇ ਕਾਰਨ ਹੌਲੀ ਹੌਲੀ ਵਿਕਸਤ ਹੋਏ ਹਨ।

ਅੰਤ ਵਿੱਚ, SiC ਪ੍ਰੋਸੈਸਿੰਗ ਸਤ੍ਹਾ ਦੀ ਗੁਣਵੱਤਾ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਲਈ ਵਾਰਪੇਜ ਅਤੇ ਖੁਰਦਰੇਪਨ ਨੂੰ ਘਟਾਉਣ ਦੀ ਇੱਕ ਹੌਲੀ-ਹੌਲੀ ਪ੍ਰਕਿਰਿਆ ਹੈ, ਜਿੱਥੇ ਹਰ ਪੜਾਅ ਦੌਰਾਨ ਸਮਤਲਤਾ ਅਤੇ ਖੁਰਦਰੇਪਨ ਨਿਯੰਤਰਣ ਮਹੱਤਵਪੂਰਨ ਹੁੰਦਾ ਹੈ।

ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀ

ਵੇਫਰ ਪੀਸਣ ਦੇ ਪੜਾਅ ਦੌਰਾਨ, ਵੇਫਰ ਨੂੰ ਲੋੜੀਂਦੀ ਸਮਤਲਤਾ ਅਤੇ ਸਤ੍ਹਾ ਦੀ ਖੁਰਦਰੀ ਤੱਕ ਪੀਸਣ ਲਈ ਵੱਖ-ਵੱਖ ਕਣਾਂ ਦੇ ਆਕਾਰਾਂ ਵਾਲੀ ਹੀਰੇ ਦੀ ਸਲਰੀ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਂਦੀ ਹੈ। ਇਸ ਤੋਂ ਬਾਅਦ ਪਾਲਿਸ਼ਿੰਗ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਨੁਕਸਾਨ-ਮੁਕਤ ਪਾਲਿਸ਼ ਕੀਤੇ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ (SiC) ਵੇਫਰ ਤਿਆਰ ਕਰਨ ਲਈ ਮਕੈਨੀਕਲ ਅਤੇ ਰਸਾਇਣਕ ਮਕੈਨੀਕਲ ਪਾਲਿਸ਼ਿੰਗ (CMP) ਤਕਨੀਕਾਂ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਂਦੀ ਹੈ।

ਪਾਲਿਸ਼ ਕਰਨ ਤੋਂ ਬਾਅਦ, SiC ਵੇਫਰਾਂ ਨੂੰ ਆਪਟੀਕਲ ਮਾਈਕ੍ਰੋਸਕੋਪ ਅਤੇ ਐਕਸ-ਰੇ ਡਿਫ੍ਰੈਕਟੋਮੀਟਰ ਵਰਗੇ ਯੰਤਰਾਂ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਸਖ਼ਤ ਗੁਣਵੱਤਾ ਨਿਰੀਖਣ ਕੀਤਾ ਜਾਂਦਾ ਹੈ ਤਾਂ ਜੋ ਇਹ ਯਕੀਨੀ ਬਣਾਇਆ ਜਾ ਸਕੇ ਕਿ ਸਾਰੇ ਤਕਨੀਕੀ ਮਾਪਦੰਡ ਲੋੜੀਂਦੇ ਮਾਪਦੰਡਾਂ ਨੂੰ ਪੂਰਾ ਕਰਦੇ ਹਨ। ਅੰਤ ਵਿੱਚ, ਪਾਲਿਸ਼ ਕੀਤੇ ਵੇਫਰਾਂ ਨੂੰ ਵਿਸ਼ੇਸ਼ ਸਫਾਈ ਏਜੰਟਾਂ ਅਤੇ ਅਤਿ-ਸ਼ੁੱਧ ਪਾਣੀ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਸਤ੍ਹਾ ਦੇ ਦੂਸ਼ਿਤ ਤੱਤਾਂ ਨੂੰ ਹਟਾਉਣ ਲਈ ਸਾਫ਼ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਫਿਰ ਉਹਨਾਂ ਨੂੰ ਅਤਿ-ਉੱਚ ਸ਼ੁੱਧਤਾ ਨਾਈਟ੍ਰੋਜਨ ਗੈਸ ਅਤੇ ਸਪਿਨ ਡ੍ਰਾਇਅਰ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਸੁਕਾਇਆ ਜਾਂਦਾ ਹੈ, ਜਿਸ ਨਾਲ ਪੂਰੀ ਉਤਪਾਦਨ ਪ੍ਰਕਿਰਿਆ ਪੂਰੀ ਹੁੰਦੀ ਹੈ।

ਸਾਲਾਂ ਦੀ ਕੋਸ਼ਿਸ਼ ਤੋਂ ਬਾਅਦ, ਚੀਨ ਦੇ ਅੰਦਰ SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਪ੍ਰੋਸੈਸਿੰਗ ਵਿੱਚ ਮਹੱਤਵਪੂਰਨ ਪ੍ਰਗਤੀ ਹੋਈ ਹੈ। ਘਰੇਲੂ ਤੌਰ 'ਤੇ, 100 mm ਡੋਪਡ ਸੈਮੀ-ਇੰਸੂਲੇਟਿੰਗ 4H-SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਸਫਲਤਾਪੂਰਵਕ ਵਿਕਸਤ ਕੀਤੇ ਗਏ ਹਨ, ਅਤੇ n-ਟਾਈਪ 4H-SiC ਅਤੇ 6H-SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਹੁਣ ਬੈਚਾਂ ਵਿੱਚ ਤਿਆਰ ਕੀਤੇ ਜਾ ਸਕਦੇ ਹਨ। TankeBlue ਅਤੇ TYST ਵਰਗੀਆਂ ਕੰਪਨੀਆਂ ਪਹਿਲਾਂ ਹੀ 150 mm SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਵਿਕਸਤ ਕਰ ਚੁੱਕੀਆਂ ਹਨ।

SiC ਵੇਫਰ ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀ ਦੇ ਮਾਮਲੇ ਵਿੱਚ, ਘਰੇਲੂ ਸੰਸਥਾਵਾਂ ਨੇ ਸ਼ੁਰੂਆਤੀ ਤੌਰ 'ਤੇ ਕ੍ਰਿਸਟਲ ਸਲਾਈਸਿੰਗ, ਪੀਸਣ ਅਤੇ ਪਾਲਿਸ਼ ਕਰਨ ਲਈ ਪ੍ਰਕਿਰਿਆ ਦੀਆਂ ਸਥਿਤੀਆਂ ਅਤੇ ਰੂਟਾਂ ਦੀ ਪੜਚੋਲ ਕੀਤੀ ਹੈ। ਉਹ ਨਮੂਨੇ ਤਿਆਰ ਕਰਨ ਦੇ ਸਮਰੱਥ ਹਨ ਜੋ ਮੂਲ ਰੂਪ ਵਿੱਚ ਡਿਵਾਈਸ ਨਿਰਮਾਣ ਲਈ ਜ਼ਰੂਰਤਾਂ ਨੂੰ ਪੂਰਾ ਕਰਦੇ ਹਨ। ਹਾਲਾਂਕਿ, ਅੰਤਰਰਾਸ਼ਟਰੀ ਮਾਪਦੰਡਾਂ ਦੇ ਮੁਕਾਬਲੇ, ਘਰੇਲੂ ਵੇਫਰਾਂ ਦੀ ਸਤਹ ਪ੍ਰੋਸੈਸਿੰਗ ਗੁਣਵੱਤਾ ਅਜੇ ਵੀ ਕਾਫ਼ੀ ਪਿੱਛੇ ਹੈ। ਕਈ ਮੁੱਦੇ ਹਨ:

ਅੰਤਰਰਾਸ਼ਟਰੀ SiC ਸਿਧਾਂਤ ਅਤੇ ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀਆਂ ਸਖ਼ਤੀ ਨਾਲ ਸੁਰੱਖਿਅਤ ਹਨ ਅਤੇ ਆਸਾਨੀ ਨਾਲ ਪਹੁੰਚਯੋਗ ਨਹੀਂ ਹਨ।

ਪ੍ਰਕਿਰਿਆ ਸੁਧਾਰ ਅਤੇ ਅਨੁਕੂਲਤਾ ਲਈ ਸਿਧਾਂਤਕ ਖੋਜ ਅਤੇ ਸਹਾਇਤਾ ਦੀ ਘਾਟ ਹੈ।

ਵਿਦੇਸ਼ੀ ਉਪਕਰਣਾਂ ਅਤੇ ਪੁਰਜ਼ਿਆਂ ਨੂੰ ਆਯਾਤ ਕਰਨ ਦੀ ਲਾਗਤ ਬਹੁਤ ਜ਼ਿਆਦਾ ਹੈ।

ਉਪਕਰਣਾਂ ਦੇ ਡਿਜ਼ਾਈਨ, ਪ੍ਰੋਸੈਸਿੰਗ ਸ਼ੁੱਧਤਾ, ਅਤੇ ਸਮੱਗਰੀ ਬਾਰੇ ਘਰੇਲੂ ਖੋਜ ਅਜੇ ਵੀ ਅੰਤਰਰਾਸ਼ਟਰੀ ਪੱਧਰ ਦੇ ਮੁਕਾਬਲੇ ਮਹੱਤਵਪੂਰਨ ਪਾੜੇ ਦਰਸਾਉਂਦੀ ਹੈ।

ਵਰਤਮਾਨ ਵਿੱਚ, ਚੀਨ ਵਿੱਚ ਵਰਤੇ ਜਾਣ ਵਾਲੇ ਜ਼ਿਆਦਾਤਰ ਉੱਚ-ਸ਼ੁੱਧਤਾ ਵਾਲੇ ਯੰਤਰ ਆਯਾਤ ਕੀਤੇ ਜਾਂਦੇ ਹਨ। ਟੈਸਟਿੰਗ ਉਪਕਰਣਾਂ ਅਤੇ ਵਿਧੀਆਂ ਵਿੱਚ ਵੀ ਹੋਰ ਸੁਧਾਰ ਦੀ ਲੋੜ ਹੈ।

ਤੀਜੀ ਪੀੜ੍ਹੀ ਦੇ ਸੈਮੀਕੰਡਕਟਰਾਂ ਦੇ ਨਿਰੰਤਰ ਵਿਕਾਸ ਦੇ ਨਾਲ, SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਸਬਸਟਰੇਟਾਂ ਦਾ ਵਿਆਸ ਲਗਾਤਾਰ ਵਧ ਰਿਹਾ ਹੈ, ਨਾਲ ਹੀ ਸਤਹ ਪ੍ਰੋਸੈਸਿੰਗ ਗੁਣਵੱਤਾ ਲਈ ਉੱਚ ਜ਼ਰੂਰਤਾਂ ਵੀ ਹਨ। SiC ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਵਾਧੇ ਤੋਂ ਬਾਅਦ ਵੇਫਰ ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀ ਸਭ ਤੋਂ ਤਕਨੀਕੀ ਤੌਰ 'ਤੇ ਚੁਣੌਤੀਪੂਰਨ ਕਦਮਾਂ ਵਿੱਚੋਂ ਇੱਕ ਬਣ ਗਈ ਹੈ।

ਪ੍ਰੋਸੈਸਿੰਗ ਵਿੱਚ ਮੌਜੂਦਾ ਚੁਣੌਤੀਆਂ ਨੂੰ ਹੱਲ ਕਰਨ ਲਈ, ਕੱਟਣ, ਪੀਸਣ ਅਤੇ ਪਾਲਿਸ਼ ਕਰਨ ਵਿੱਚ ਸ਼ਾਮਲ ਵਿਧੀਆਂ ਦਾ ਹੋਰ ਅਧਿਐਨ ਕਰਨਾ ਅਤੇ SiC ਵੇਫਰ ਨਿਰਮਾਣ ਲਈ ਢੁਕਵੇਂ ਪ੍ਰਕਿਰਿਆ ਤਰੀਕਿਆਂ ਅਤੇ ਰੂਟਾਂ ਦੀ ਪੜਚੋਲ ਕਰਨਾ ਜ਼ਰੂਰੀ ਹੈ। ਇਸ ਦੇ ਨਾਲ ਹੀ, ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੇ ਸਬਸਟਰੇਟ ਪੈਦਾ ਕਰਨ ਲਈ ਉੱਨਤ ਅੰਤਰਰਾਸ਼ਟਰੀ ਪ੍ਰੋਸੈਸਿੰਗ ਤਕਨਾਲੋਜੀਆਂ ਤੋਂ ਸਿੱਖਣਾ ਅਤੇ ਅਤਿ-ਆਧੁਨਿਕ ਅਤਿ-ਸ਼ੁੱਧਤਾ ਮਸ਼ੀਨਿੰਗ ਤਕਨੀਕਾਂ ਅਤੇ ਉਪਕਰਣਾਂ ਨੂੰ ਅਪਣਾਉਣਾ ਜ਼ਰੂਰੀ ਹੈ।

ਜਿਵੇਂ-ਜਿਵੇਂ ਵੇਫਰ ਦਾ ਆਕਾਰ ਵਧਦਾ ਹੈ, ਕ੍ਰਿਸਟਲ ਵਾਧੇ ਅਤੇ ਪ੍ਰੋਸੈਸਿੰਗ ਦੀ ਮੁਸ਼ਕਲ ਵੀ ਵਧਦੀ ਹੈ। ਹਾਲਾਂਕਿ, ਡਾਊਨਸਟ੍ਰੀਮ ਡਿਵਾਈਸਾਂ ਦੀ ਨਿਰਮਾਣ ਕੁਸ਼ਲਤਾ ਵਿੱਚ ਕਾਫ਼ੀ ਸੁਧਾਰ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਯੂਨਿਟ ਦੀ ਲਾਗਤ ਘੱਟ ਜਾਂਦੀ ਹੈ। ਵਰਤਮਾਨ ਵਿੱਚ, ਮੁੱਖ SiC ਵੇਫਰ ਸਪਲਾਇਰ ਵਿਸ਼ਵ ਪੱਧਰ 'ਤੇ 4 ਇੰਚ ਤੋਂ 6 ਇੰਚ ਵਿਆਸ ਦੇ ਉਤਪਾਦ ਪੇਸ਼ ਕਰਦੇ ਹਨ। ਕ੍ਰੀ ਅਤੇ II-VI ਵਰਗੀਆਂ ਪ੍ਰਮੁੱਖ ਕੰਪਨੀਆਂ ਨੇ ਪਹਿਲਾਂ ਹੀ 8-ਇੰਚ SiC ਵੇਫਰ ਉਤਪਾਦਨ ਲਾਈਨਾਂ ਦੇ ਵਿਕਾਸ ਲਈ ਯੋਜਨਾਬੰਦੀ ਸ਼ੁਰੂ ਕਰ ਦਿੱਤੀ ਹੈ।

ਪੋਸਟ ਸਮਾਂ: ਮਈ-23-2025