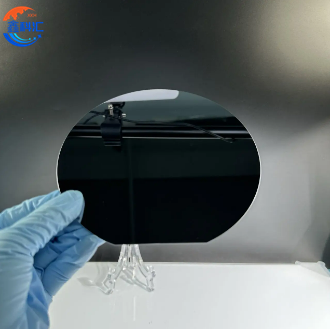

ਸਿਲੀਕਾਨ ਵੇਫਰ ਸਬਸਟਰੇਟ 'ਤੇ ਸਿਲੀਕਾਨ ਪਰਮਾਣੂਆਂ ਦੀ ਇੱਕ ਵਾਧੂ ਪਰਤ ਉਗਾਉਣ ਦੇ ਕਈ ਫਾਇਦੇ ਹਨ:

CMOS ਸਿਲੀਕਾਨ ਪ੍ਰਕਿਰਿਆਵਾਂ ਵਿੱਚ, ਵੇਫਰ ਸਬਸਟਰੇਟ 'ਤੇ ਐਪੀਟੈਕਸੀਅਲ ਵਿਕਾਸ (EPI) ਇੱਕ ਮਹੱਤਵਪੂਰਨ ਪ੍ਰਕਿਰਿਆ ਕਦਮ ਹੈ।

1, ਕ੍ਰਿਸਟਲ ਗੁਣਵੱਤਾ ਵਿੱਚ ਸੁਧਾਰ

ਸ਼ੁਰੂਆਤੀ ਸਬਸਟਰੇਟ ਨੁਕਸ ਅਤੇ ਅਸ਼ੁੱਧੀਆਂ: ਨਿਰਮਾਣ ਪ੍ਰਕਿਰਿਆ ਦੌਰਾਨ, ਵੇਫਰ ਸਬਸਟਰੇਟ ਵਿੱਚ ਕੁਝ ਨੁਕਸ ਅਤੇ ਅਸ਼ੁੱਧੀਆਂ ਹੋ ਸਕਦੀਆਂ ਹਨ। ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦਾ ਵਾਧਾ ਸਬਸਟਰੇਟ 'ਤੇ ਨੁਕਸ ਅਤੇ ਅਸ਼ੁੱਧੀਆਂ ਦੀ ਘੱਟ ਗਾੜ੍ਹਾਪਣ ਦੇ ਨਾਲ ਇੱਕ ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੀ ਮੋਨੋਕ੍ਰਿਸਟਲਾਈਨ ਸਿਲੀਕਾਨ ਪਰਤ ਪੈਦਾ ਕਰ ਸਕਦਾ ਹੈ, ਜੋ ਕਿ ਬਾਅਦ ਦੇ ਡਿਵਾਈਸ ਨਿਰਮਾਣ ਲਈ ਮਹੱਤਵਪੂਰਨ ਹੈ।

ਇਕਸਾਰ ਕ੍ਰਿਸਟਲ ਬਣਤਰ: ਐਪੀਟੈਕਸੀਅਲ ਵਾਧਾ ਇੱਕ ਵਧੇਰੇ ਇਕਸਾਰ ਕ੍ਰਿਸਟਲ ਬਣਤਰ ਨੂੰ ਯਕੀਨੀ ਬਣਾਉਂਦਾ ਹੈ, ਅਨਾਜ ਦੀਆਂ ਸੀਮਾਵਾਂ ਦੇ ਪ੍ਰਭਾਵ ਅਤੇ ਸਬਸਟਰੇਟ ਸਮੱਗਰੀ ਵਿੱਚ ਨੁਕਸ ਨੂੰ ਘਟਾਉਂਦਾ ਹੈ, ਜਿਸ ਨਾਲ ਵੇਫਰ ਦੀ ਸਮੁੱਚੀ ਕ੍ਰਿਸਟਲ ਗੁਣਵੱਤਾ ਵਿੱਚ ਸੁਧਾਰ ਹੁੰਦਾ ਹੈ।

2, ਬਿਜਲੀ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਵਿੱਚ ਸੁਧਾਰ।

ਡਿਵਾਈਸ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਨੂੰ ਅਨੁਕੂਲ ਬਣਾਉਣਾ: ਸਬਸਟਰੇਟ 'ਤੇ ਇੱਕ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਨੂੰ ਵਧਾ ਕੇ, ਡੋਪਿੰਗ ਗਾੜ੍ਹਾਪਣ ਅਤੇ ਸਿਲੀਕਾਨ ਦੀ ਕਿਸਮ ਨੂੰ ਸਹੀ ਢੰਗ ਨਾਲ ਨਿਯੰਤਰਿਤ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ, ਡਿਵਾਈਸ ਦੇ ਇਲੈਕਟ੍ਰੀਕਲ ਪ੍ਰਦਰਸ਼ਨ ਨੂੰ ਅਨੁਕੂਲ ਬਣਾਉਂਦਾ ਹੈ। ਉਦਾਹਰਣ ਵਜੋਂ, ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਡੋਪਿੰਗ ਨੂੰ MOSFETs ਅਤੇ ਹੋਰ ਇਲੈਕਟ੍ਰੀਕਲ ਮਾਪਦੰਡਾਂ ਦੇ ਥ੍ਰੈਸ਼ਹੋਲਡ ਵੋਲਟੇਜ ਨੂੰ ਨਿਯੰਤਰਿਤ ਕਰਨ ਲਈ ਬਾਰੀਕੀ ਨਾਲ ਐਡਜਸਟ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ।

ਲੀਕੇਜ ਕਰੰਟ ਨੂੰ ਘਟਾਉਣਾ: ਇੱਕ ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੀ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਵਿੱਚ ਘੱਟ ਨੁਕਸ ਘਣਤਾ ਹੁੰਦੀ ਹੈ, ਜੋ ਡਿਵਾਈਸਾਂ ਵਿੱਚ ਲੀਕੇਜ ਕਰੰਟ ਨੂੰ ਘਟਾਉਣ ਵਿੱਚ ਮਦਦ ਕਰਦੀ ਹੈ, ਜਿਸ ਨਾਲ ਡਿਵਾਈਸ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਅਤੇ ਭਰੋਸੇਯੋਗਤਾ ਵਿੱਚ ਸੁਧਾਰ ਹੁੰਦਾ ਹੈ।

3, ਬਿਜਲੀ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਵਿੱਚ ਸੁਧਾਰ।

ਵਿਸ਼ੇਸ਼ਤਾ ਦਾ ਆਕਾਰ ਘਟਾਉਣਾ: ਛੋਟੇ ਪ੍ਰਕਿਰਿਆ ਨੋਡਾਂ (ਜਿਵੇਂ ਕਿ 7nm, 5nm) ਵਿੱਚ, ਡਿਵਾਈਸਾਂ ਦਾ ਵਿਸ਼ੇਸ਼ਤਾ ਆਕਾਰ ਸੁੰਗੜਦਾ ਰਹਿੰਦਾ ਹੈ, ਜਿਸ ਲਈ ਵਧੇਰੇ ਸ਼ੁੱਧ ਅਤੇ ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੀ ਸਮੱਗਰੀ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਐਪੀਟੈਕਸੀਅਲ ਵਿਕਾਸ ਤਕਨਾਲੋਜੀ ਇਹਨਾਂ ਮੰਗਾਂ ਨੂੰ ਪੂਰਾ ਕਰ ਸਕਦੀ ਹੈ, ਉੱਚ-ਪ੍ਰਦਰਸ਼ਨ ਅਤੇ ਉੱਚ-ਘਣਤਾ ਵਾਲੇ ਏਕੀਕ੍ਰਿਤ ਸਰਕਟਾਂ ਦੇ ਨਿਰਮਾਣ ਦਾ ਸਮਰਥਨ ਕਰਦੀ ਹੈ।

ਬ੍ਰੇਕਡਾਊਨ ਵੋਲਟੇਜ ਨੂੰ ਵਧਾਉਣਾ: ਐਪੀਟੈਕਸੀਅਲ ਪਰਤਾਂ ਨੂੰ ਉੱਚ ਬ੍ਰੇਕਡਾਊਨ ਵੋਲਟੇਜ ਨਾਲ ਡਿਜ਼ਾਈਨ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ, ਜੋ ਕਿ ਉੱਚ-ਪਾਵਰ ਅਤੇ ਉੱਚ-ਵੋਲਟੇਜ ਡਿਵਾਈਸਾਂ ਦੇ ਨਿਰਮਾਣ ਲਈ ਮਹੱਤਵਪੂਰਨ ਹੈ। ਉਦਾਹਰਣ ਵਜੋਂ, ਪਾਵਰ ਡਿਵਾਈਸਾਂ ਵਿੱਚ, ਐਪੀਟੈਕਸੀਅਲ ਪਰਤਾਂ ਡਿਵਾਈਸ ਦੇ ਬ੍ਰੇਕਡਾਊਨ ਵੋਲਟੇਜ ਨੂੰ ਬਿਹਤਰ ਬਣਾ ਸਕਦੀਆਂ ਹਨ, ਸੁਰੱਖਿਅਤ ਓਪਰੇਟਿੰਗ ਰੇਂਜ ਨੂੰ ਵਧਾਉਂਦੀਆਂ ਹਨ।

4, ਪ੍ਰਕਿਰਿਆ ਅਨੁਕੂਲਤਾ ਅਤੇ ਬਹੁ-ਪਰਤ ਢਾਂਚੇ

ਮਲਟੀਲੇਅਰ ਸਟ੍ਰਕਚਰ: ਐਪੀਟੈਕਸੀਅਲ ਗ੍ਰੋਥ ਟੈਕਨਾਲੋਜੀ ਸਬਸਟਰੇਟਾਂ 'ਤੇ ਮਲਟੀਲੇਅਰ ਸਟ੍ਰਕਚਰ ਦੇ ਵਾਧੇ ਦੀ ਆਗਿਆ ਦਿੰਦੀ ਹੈ, ਵੱਖ-ਵੱਖ ਪਰਤਾਂ ਵਿੱਚ ਵੱਖ-ਵੱਖ ਡੋਪਿੰਗ ਗਾੜ੍ਹਾਪਣ ਅਤੇ ਕਿਸਮਾਂ ਹੁੰਦੀਆਂ ਹਨ। ਇਹ ਗੁੰਝਲਦਾਰ CMOS ਡਿਵਾਈਸਾਂ ਦੇ ਨਿਰਮਾਣ ਅਤੇ ਤਿੰਨ-ਅਯਾਮੀ ਏਕੀਕਰਨ ਨੂੰ ਸਮਰੱਥ ਬਣਾਉਣ ਲਈ ਬਹੁਤ ਲਾਭਦਾਇਕ ਹੈ।

ਅਨੁਕੂਲਤਾ: ਐਪੀਟੈਕਸੀਅਲ ਵਿਕਾਸ ਪ੍ਰਕਿਰਿਆ ਮੌਜੂਦਾ CMOS ਨਿਰਮਾਣ ਪ੍ਰਕਿਰਿਆਵਾਂ ਦੇ ਨਾਲ ਬਹੁਤ ਅਨੁਕੂਲ ਹੈ, ਜਿਸ ਨਾਲ ਪ੍ਰਕਿਰਿਆ ਲਾਈਨਾਂ ਵਿੱਚ ਮਹੱਤਵਪੂਰਨ ਸੋਧਾਂ ਦੀ ਲੋੜ ਤੋਂ ਬਿਨਾਂ ਮੌਜੂਦਾ ਨਿਰਮਾਣ ਕਾਰਜ ਪ੍ਰਵਾਹ ਵਿੱਚ ਏਕੀਕ੍ਰਿਤ ਕਰਨਾ ਆਸਾਨ ਹੋ ਜਾਂਦਾ ਹੈ।

ਸੰਖੇਪ: CMOS ਸਿਲੀਕਾਨ ਪ੍ਰਕਿਰਿਆਵਾਂ ਵਿੱਚ ਐਪੀਟੈਕਸੀਅਲ ਵਾਧੇ ਦੀ ਵਰਤੋਂ ਮੁੱਖ ਤੌਰ 'ਤੇ ਵੇਫਰ ਕ੍ਰਿਸਟਲ ਗੁਣਵੱਤਾ ਨੂੰ ਵਧਾਉਣਾ, ਡਿਵਾਈਸ ਇਲੈਕਟ੍ਰੀਕਲ ਪ੍ਰਦਰਸ਼ਨ ਨੂੰ ਅਨੁਕੂਲ ਬਣਾਉਣਾ, ਉੱਨਤ ਪ੍ਰਕਿਰਿਆ ਨੋਡਾਂ ਦਾ ਸਮਰਥਨ ਕਰਨਾ, ਅਤੇ ਉੱਚ-ਪ੍ਰਦਰਸ਼ਨ ਅਤੇ ਉੱਚ-ਘਣਤਾ ਵਾਲੇ ਏਕੀਕ੍ਰਿਤ ਸਰਕਟ ਨਿਰਮਾਣ ਦੀਆਂ ਮੰਗਾਂ ਨੂੰ ਪੂਰਾ ਕਰਨਾ ਹੈ। ਐਪੀਟੈਕਸੀਅਲ ਵਾਧੇ ਤਕਨਾਲੋਜੀ ਸਮੱਗਰੀ ਡੋਪਿੰਗ ਅਤੇ ਬਣਤਰ ਦੇ ਸਹੀ ਨਿਯੰਤਰਣ ਦੀ ਆਗਿਆ ਦਿੰਦੀ ਹੈ, ਡਿਵਾਈਸਾਂ ਦੀ ਸਮੁੱਚੀ ਕਾਰਗੁਜ਼ਾਰੀ ਅਤੇ ਭਰੋਸੇਯੋਗਤਾ ਵਿੱਚ ਸੁਧਾਰ ਕਰਦੀ ਹੈ।

ਪੋਸਟ ਸਮਾਂ: ਅਕਤੂਬਰ-16-2024